R5F61665N50FPV Renesas Electronics America, R5F61665N50FPV Datasheet - Page 849

R5F61665N50FPV

Manufacturer Part Number

R5F61665N50FPV

Description

MCU FLASH 512K ROM 144-LQFP

Manufacturer

Renesas Electronics America

Series

H8® H8SX/1600r

Datasheet

1.R5F61665N50FPV.pdf

(1492 pages)

Specifications of R5F61665N50FPV

Core Processor

H8SX

Core Size

16/32-Bit

Speed

50MHz

Connectivity

EBI/EMI, I²C, IrDA, SCI, SmartCard, USB

Peripherals

DMA, LVD, POR, PWM, WDT

Number Of I /o

92

Program Memory Size

512KB (512K x 8)

Program Memory Type

FLASH

Ram Size

40K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 3.6 V

Data Converters

A/D 8x10b; D/A 2x8b

Oscillator Type

External

Operating Temperature

-20°C ~ 75°C

Package / Case

144-LQFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

R5F61665N50FPV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 849 of 1492

- Download datasheet (8Mb)

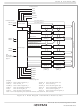

Notes: 1. To use an external reset or external clock, the DDR and ICR bits in the corresponding

Bit

6

5

4

3

2

1

0

2. In unit 2 and unit 3, one interrupt signal is used for CMIEB or CMIEA. For details, see

3. Available only in unit 0 and unit 1.

Bit Name

CMIEA

OVIE

CCLR1

CCLR0

CKS2

CKS1

CKS0

pin should be set to 0 and 1, respectively. For details, see section 13, I/O Ports.

section 16.7, Interrupt Sources.

Initial

Value

0

0

0

0

0

0

0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Compare Match Interrupt Enable A

Timer Overflow Interrupt Enable*

Description

Selects whether CMFA interrupt requests (CMIA) are

enabled or disabled when the CMFA flag in TCSR is set

to 1. *

0: CMFA interrupt requests (CMIA) are disabled

1: CMFA interrupt requests (CMIA) are enabled

Selects whether OVF interrupt requests (OVI) are

enabled or disabled when the OVF flag in TCSR is set to

1.

0: OVF interrupt requests (OVI) are disabled

1: OVF interrupt requests (OVI) are enabled

Counter Clear 1 and 0*

These bits select the method by which TCNT is cleared.

00: Clearing is disabled

01: Cleared by compare match A

10: Cleared by compare match B

11: Cleared at rising edge (TMRIS in TCCR is cleared to

Clock Select 2 to 0*

These bits select the clock input to TCNT and count

condition. See table 16.2.

0) of the external reset input or when the external

reset input is high (TMRIS in TCCR is set to 1) *

2

Rev. 2.00 Oct. 21, 2009 Page 815 of 1454

1

1

Section 16 8-Bit Timers (TMR)

3

REJ09B0498-0200

3

Related parts for R5F61665N50FPV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: