R5F61665N50FPV Renesas Electronics America, R5F61665N50FPV Datasheet - Page 607

R5F61665N50FPV

Manufacturer Part Number

R5F61665N50FPV

Description

MCU FLASH 512K ROM 144-LQFP

Manufacturer

Renesas Electronics America

Series

H8® H8SX/1600r

Datasheet

1.R5F61665N50FPV.pdf

(1492 pages)

Specifications of R5F61665N50FPV

Core Processor

H8SX

Core Size

16/32-Bit

Speed

50MHz

Connectivity

EBI/EMI, I²C, IrDA, SCI, SmartCard, USB

Peripherals

DMA, LVD, POR, PWM, WDT

Number Of I /o

92

Program Memory Size

512KB (512K x 8)

Program Memory Type

FLASH

Ram Size

40K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 3.6 V

Data Converters

A/D 8x10b; D/A 2x8b

Oscillator Type

External

Operating Temperature

-20°C ~ 75°C

Package / Case

144-LQFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

R5F61665N50FPV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 607 of 1492

- Download datasheet (8Mb)

Table 12.3 Chain Transfer Conditions

Notes: 1. CRA in normal mode transfer, CRAL in repeat transfer mode, or CRB in block transfer

12.5.1

When the transfer data size is word and the SAR and DAR values are not a multiple of 2, the bus

cycle is divided and the transfer data is read from or written to in bytes. Similarly, when the

transfer data size is longword and the SAR and DAR values are not a multiple of 4, the bus cycle

is divided and the transfer data is read from or written to in words.

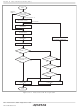

Table 12.4 shows the relationship among, SAR, DAR, transfer data size, bus cycle divisions, and

access data size. Figure 12.5 shows the bus cycle division example.

Table 12.4 Number of Bus Cycle Divisions and Access Size

CHNE CHNS DISEL

0

0

0

1

1

1

1

SAR and DAR Values Byte (B)

Address 4n

Address 2n + 1

Address 4n + 2

2. When the contents of the CRAH is written to the CRAL in repeat transfer mode

⎯

⎯

⎯

0

1

1

1

Bus Cycle Division

1st Transfer

mode

0

0

1

⎯

0

⎯

1

Transfer

Counter*

Not 0

0*

⎯

Not 0

0*

Not 0

1 (B)

1 (B)

1 (B)

2

2

1

CHNE CHNS DISEL

⎯

⎯

⎯

0

0

0

⎯

0

0

0

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

2nd Transfer

Word (W)

1 (W)

2 (B-B)

1 (W)

Specified Data Size

⎯

⎯

⎯

0

0

1

0

0

1

⎯

Section 12 Data Transfer Controller (DTC)

Rev. 2.00 Oct. 21, 2009 Page 573 of 1454

Transfer

Counter*

⎯

⎯

⎯

Not 0

0*

⎯

⎯

Not 0

0*

⎯

2

2

1

DTC Transfer

Ends at 1st transfer

Ends at 1st transfer

Interrupt request to CPU

Ends at 2nd transfer

Ends at 2nd transfer

Interrupt request to CPU

Ends at 1st transfer

Ends at 2nd transfer

Ends at 2nd transfer

Interrupt request to CPU

Ends at 1st transfer

Interrupt request to CPU

Longword (LW)

1 (LW)

3 (B-W-B)

2 (W-W)

REJ09B0498-0200

Related parts for R5F61665N50FPV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: