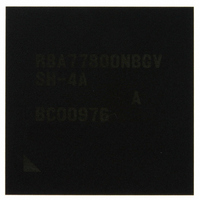

R8A77800ANBGAV Renesas Electronics America, R8A77800ANBGAV Datasheet - Page 654

R8A77800ANBGAV

Manufacturer Part Number

R8A77800ANBGAV

Description

IC SUPERH MPU ROMLESS 449-BGA

Manufacturer

Renesas Electronics America

Series

SuperH® SH7780r

Datasheet

1.R8A77800ANBGV.pdf

(1342 pages)

Specifications of R8A77800ANBGAV

Core Processor

SH-4A

Core Size

32-Bit

Speed

400MHz

Connectivity

Audio Codec, MMC, Serial Sound, SCI, SIO, SPI, SSI

Peripherals

DMA, POR, WDT

Number Of I /o

75

Program Memory Type

ROMless

Ram Size

16K x 8

Voltage - Supply (vcc/vdd)

1.15 V ~ 1.35 V

Oscillator Type

External

Operating Temperature

-20°C ~ 75°C

Package / Case

449-BGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Data Converters

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

R8A77800ANBGAV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 654 of 1342

- Download datasheet (7Mb)

Section 14 Direct Memory Access Controller (DMAC)

In round-robin mode, the priority changes according to the specification shown in figure 14.2.

However, the channel in cycle steal mode cannot be mixed with the channel in burst mode.

14.4.4

After the DMA source address registers (SAR), DMA destination address registers (DAR), DMA

transfer count registers (DMATCR), DMA channel control registers (CHCR), DMA operation

register (DMAOR), and DMA extended resource selectors (DMARS) are set, the DMAC transfers

data according to the following procedure:

1. Checks to see if transfer is enabled (DE = 1, DME = 1, TE = 0, AE = 0, NMIF = 0)

2. When a transfer request occurs while transfer is enabled, the DMAC transfers one transfer unit

3. When the specified number of transfer have been completed (when DMATCR reaches 0), the

4. When an address error or an NMI interrupt is generated, the transfer is aborted. Transfers are

Figure 14.11 shows a flowchart of this procedure.

Rev.1.00 Dec. 13, 2005 Page 602 of 1286

REJ09B0158-0100

CH0 transfer

source

CH1 transfer

source

SuperHyway

bus cycle

of data (depending on the TS0 and TS1 settings). In auto request mode, the transfer begins

automatically when the DE bit and DME bit are set to 1. The DMATCR value will be

decremented for each transfer. The actual transfer flows vary by address mode and bus mode.

transfer ends normally. If the IE bit in CHCR is set to 1 at this time, a DMINT interrupt is sent

to the CPU.

also aborted when the DE bit in CHCR or the DME bit in DMAOR is changed to 0.

DMA Transfer Flow

Priority:

CH0:

CH1:

Figure 14.10 Bus State when Multiple Channels are Operating

CPU

CH0 > CH1

Cycle steal mode

Burst mode

DMA CH1

Burst mode

DMA CH1

DMA CH1

DMA CH0

DMA CH0 and CH1

Burst mode

DMA CH1

DMA CH0

DMA CH1

Burst mode

DMA CH1

DMA CH1

CPU

Related parts for R8A77800ANBGAV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: