R8A77800ANBGAV Renesas Electronics America, R8A77800ANBGAV Datasheet - Page 46

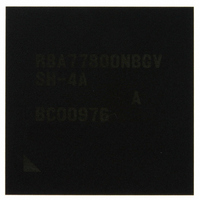

R8A77800ANBGAV

Manufacturer Part Number

R8A77800ANBGAV

Description

IC SUPERH MPU ROMLESS 449-BGA

Manufacturer

Renesas Electronics America

Series

SuperH® SH7780r

Datasheet

1.R8A77800ANBGV.pdf

(1342 pages)

Specifications of R8A77800ANBGAV

Core Processor

SH-4A

Core Size

32-Bit

Speed

400MHz

Connectivity

Audio Codec, MMC, Serial Sound, SCI, SIO, SPI, SSI

Peripherals

DMA, POR, WDT

Number Of I /o

75

Program Memory Type

ROMless

Ram Size

16K x 8

Voltage - Supply (vcc/vdd)

1.15 V ~ 1.35 V

Oscillator Type

External

Operating Temperature

-20°C ~ 75°C

Package / Case

449-BGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Data Converters

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

R8A77800ANBGAV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 46 of 1342

- Download datasheet (7Mb)

Section 7 Memory Management Unit (MMU)

Table 7.1

Table 7.2

Section 8 Caches

Table 8.1

Table 8.2

Table 8.3

Table 8.4

Section 9 L Memory

Table 9.1

Table 9.2

Table 9.3

Table 9.4

Section 10 Interrupt Controller (INTC)

Table 10.1

Table 10.2

Table 10.3

Table 10.4

Table 10.5

Table 10.6

Table 10.7

Table 10.8

Table 10.9

Table 10.10

Table 10.11

Table 10.12

Table 10.13

Table 10.14

Section 11 Local Bus State Controller (LBSC)

Table 11.1

Table 11.2

Table 11.3

Table 11.4

Table 11.5

Table 11.6

Table 11.7

Table 11.8

Table 11.9

Rev.1.00 Dec. 13, 2005 Page xliv of l

Register Configuration.......................................................................................... 156

Register States in Each Processing State .............................................................. 156

Cache Features...................................................................................................... 197

Store Queue Features ............................................................................................ 197

Register Configuration.......................................................................................... 200

Register States in Each Processing State .............................................................. 200

L Memory Addresses............................................................................................ 227

Register Configuration.......................................................................................... 228

Register Status in Each Processing State .............................................................. 228

Protective Function Exceptions to Access L Memory.......................................... 240

Interrupt Types...................................................................................................... 246

INTC Pin Configuration ....................................................................................... 250

INTC Register Configuration ............................................................................... 251

Register States in Each Operating Mode .............................................................. 253

Interrupt Request Sources and INT2PRI0 to INT2PRI7....................................... 276

Correspondence between Bits in INT2A0 and Sources ........................................ 277

Correspondence between Bits in INT2A1 and Sources ........................................ 280

Correspondence between Bits in INT2MSKR and Interrupt Masking ................. 283

Correspondence between Bits in INT2MSKCR and Interrupt Mask Clearing ..... 285

Pin Configuration.................................................................................................. 318

LBSC External Memory Space Map .................................................................... 322

Correspondence Between External Pins (MODE4 and MODE3)......................... 324

Correspondence Between External Pin (MODE5) and Endian ............................ 325

PCMCIA Interface Features ................................................................................. 325

PCMCIA Support Interface .................................................................................. 326

Register Configuration.......................................................................................... 329

Register State in Each Processing Mode............................................................... 330

32-Bit External Device/Big-Endian Access and Data Alignment......................... 353

Correspondence between Interrupt Input Pins and Bits in INT2GPIC ............. 295

IRL[3:0], IRL[7:4] Pins and Interrupt Levels ................................................... 298

Interrupt Exception Handling and Priority........................................................ 302

Interrupt Response Time................................................................................... 311

Switching Sequence of IRQ/IRL[7:0] Pin Function ......................................... 313

Related parts for R8A77800ANBGAV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: