DF2134AFA20V Renesas Electronics America, DF2134AFA20V Datasheet - Page 593

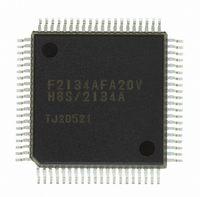

DF2134AFA20V

Manufacturer Part Number

DF2134AFA20V

Description

IC H8S/2100 MCU FLASH 80QFP

Manufacturer

Renesas Electronics America

Series

H8® H8S/2100r

Datasheets

1.HEWH8E10A.pdf

(19 pages)

2.D12312SVTE25V.pdf

(341 pages)

3.DF2134AFA20V.pdf

(1063 pages)

Specifications of DF2134AFA20V

Core Processor

H8S/2000

Core Size

16-Bit

Speed

20MHz

Connectivity

IrDA, SCI

Peripherals

POR, PWM, WDT

Number Of I /o

58

Program Memory Size

128KB (128K x 8)

Program Memory Type

FLASH

Ram Size

4K x 8

Voltage - Supply (vcc/vdd)

4 V ~ 5.5 V

Data Converters

A/D 8x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-20°C ~ 75°C

Package / Case

80-QFP

For Use With

3DK2166 - DEV EVAL KIT H8S/2166

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2134AFA20V

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 593 of 1063

- Download datasheet (6Mb)

Table 17.6 Host Interface Operation

17.3.3

The A20 gate signal can mask address A20 to emulate an addressing mode used by personal

computers with an 8086 * -family CPU. In slave mode, a regular-speed A20 gate signal can be

output under firmware control, or a fast A20 gate signal can be output under hardware control.

Fast A20 gate output is enabled by setting the FGA20E bit (bit 0) to 1 in HICR (H'FFF0).

Note: * Intel microprocessor.

Regular A20 Gate Operation: Output of the A20 gate signal can be controlled by an H'D1

command followed by data. When the slave processor receives data, it normally uses an interrupt

routine activated by the IBF1 interrupt to read IDR1. If the data follows an H'D1 command,

software copies bit 1 of the data and outputs it at the gate A20 pin.

Fast A20 Gate Operation: When the FGA20E bit is set to 1, P81/GA20 is used for output of a

fast A20 gate signal. Bit P81DDR must be set to 1 to assign this pin for output. The initial output

from this pin will be a logic 1, which is the initial value. Afterward, the host processor can

manipulate the output from this pin by sending commands and data. This function is available

CS2

CS2

CS2

CS2

1

0

CS1

CS1

0

1

CS1

CS1

A20 Gate

IOR

IOR

IOR

IOR

0

1

0

1

IOW

IOW

IOW

IOW

0

1

0

1

0

1

0

1

HA0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Operation

Setting prohibited

Setting prohibited

Data read from output data register 1 (ODR1)

Status read from status register 1 (STR1)

Data write to input data register 1 (IDR1)

Command write to input data register 1 (IDR1)

Idle state

Idle state

Setting prohibited

Setting prohibited

Data read from output data register 2 (ODR2)

Status read from status register 2 (STR2)

Data write to input data register 2 (IDR2)

Command write to input data register 2 (IDR2)

Idle state

Idle state

Section 17 Host Interface [H8S/2138 Group]

Rev. 4.00 Jun 06, 2006 page 537 of 1004

REJ09B0301-0400

Related parts for DF2134AFA20V

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: