DF2134AFA20V Renesas Electronics America, DF2134AFA20V Datasheet - Page 28

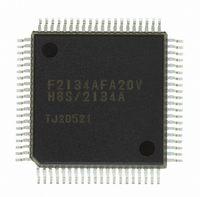

DF2134AFA20V

Manufacturer Part Number

DF2134AFA20V

Description

IC H8S/2100 MCU FLASH 80QFP

Manufacturer

Renesas Electronics America

Series

H8® H8S/2100r

Datasheets

1.HEWH8E10A.pdf

(19 pages)

2.D12312SVTE25V.pdf

(341 pages)

3.DF2134AFA20V.pdf

(1063 pages)

Specifications of DF2134AFA20V

Core Processor

H8S/2000

Core Size

16-Bit

Speed

20MHz

Connectivity

IrDA, SCI

Peripherals

POR, PWM, WDT

Number Of I /o

58

Program Memory Size

128KB (128K x 8)

Program Memory Type

FLASH

Ram Size

4K x 8

Voltage - Supply (vcc/vdd)

4 V ~ 5.5 V

Data Converters

A/D 8x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-20°C ~ 75°C

Package / Case

80-QFP

For Use With

3DK2166 - DEV EVAL KIT H8S/2166

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2134AFA20V

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 28 of 1063

- Download datasheet (6Mb)

14.4 Interrupts ........................................................................................................................... 384

14.5 Usage Notes ...................................................................................................................... 384

Section 15 Serial Communication Interface (SCI, IrDA)

15.1 Overview........................................................................................................................... 387

15.2 Register Descriptions ........................................................................................................ 392

15.3 Operation .......................................................................................................................... 417

15.4 SCI Interrupts.................................................................................................................... 450

15.5 Usage Notes ...................................................................................................................... 451

Section 16 I

16.1 Overview........................................................................................................................... 455

Rev. 4.00 Jun 06, 2006 page xxvi of liv

14.3.3 Timing of Setting of Overflow Flag (OVF) ......................................................... 383

14.5.1 Contention between Timer Counter (TCNT) Write and Increment ..................... 384

14.5.2 Changing Value of CKS2 to CKS0...................................................................... 385

14.5.3 Switching between Watchdog Timer Mode and Interval Timer Mode................ 385

14.5.4 Counter Value in Transitions between High-Speed Mode, Subactive Mode,

14.5.5 OVF Flag Clear Condition................................................................................... 386

15.1.1 Features................................................................................................................ 387

15.1.2 Block Diagram ..................................................................................................... 389

15.1.3 Pin Configuration................................................................................................. 390

15.1.4 Register Configuration......................................................................................... 390

15.2.1 Receive Shift Register (RSR) .............................................................................. 392

15.2.2 Receive Data Register (RDR) .............................................................................. 392

15.2.3 Transmit Shift Register (TSR) ............................................................................. 393

15.2.4 Transmit Data Register (TDR)............................................................................. 393

15.2.5 Serial Mode Register (SMR)................................................................................ 394

15.2.6 Serial Control Register (SCR).............................................................................. 397

15.2.7 Serial Status Register (SSR) ................................................................................ 401

15.2.8 Bit Rate Register (BRR) ...................................................................................... 405

15.2.9 Serial Interface Mode Register (SCMR).............................................................. 413

15.2.10 Module Stop Control Register (MSTPCR) .......................................................... 414

15.2.11 Keyboard Comparator Control Register (KBCOMP) .......................................... 416

15.3.1 Overview.............................................................................................................. 417

15.3.2 Operation in Asynchronous Mode ....................................................................... 419

15.3.3 Multiprocessor Communication Function............................................................ 430

15.3.4 Operation in Synchronous Mode ......................................................................... 438

15.3.5 IrDA Operation .................................................................................................... 447

16.1.1 Features................................................................................................................ 455

16.1.2 Block Diagram ..................................................................................................... 456

and Watch Mode.................................................................................................. 385

2

C Bus Interface [H8S/2138 Group Option]

......................................... 455

........................................ 387

Related parts for DF2134AFA20V

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: