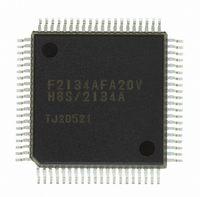

DF2134AFA20V Renesas Electronics America, DF2134AFA20V Datasheet - Page 171

DF2134AFA20V

Manufacturer Part Number

DF2134AFA20V

Description

IC H8S/2100 MCU FLASH 80QFP

Manufacturer

Renesas Electronics America

Series

H8® H8S/2100r

Datasheets

1.HEWH8E10A.pdf

(19 pages)

2.D12312SVTE25V.pdf

(341 pages)

3.DF2134AFA20V.pdf

(1063 pages)

Specifications of DF2134AFA20V

Core Processor

H8S/2000

Core Size

16-Bit

Speed

20MHz

Connectivity

IrDA, SCI

Peripherals

POR, PWM, WDT

Number Of I /o

58

Program Memory Size

128KB (128K x 8)

Program Memory Type

FLASH

Ram Size

4K x 8

Voltage - Supply (vcc/vdd)

4 V ~ 5.5 V

Data Converters

A/D 8x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-20°C ~ 75°C

Package / Case

80-QFP

For Use With

3DK2166 - DEV EVAL KIT H8S/2166

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2134AFA20V

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 171 of 1063

- Download datasheet (6Mb)

Interrupts KIN7 to KIN0: Interrupts KIN7 to KIN0 are requested by input signals at pins KIN7

to KIN0. When any of pins KIN7 to KIN0 are used as key-sense inputs, the corresponding

KMIMR bits should be cleared to 0 to enable those key-sense input interrupts. The remaining

unused key-sense input KMIMR bits should be set to 1 to disable those interrupts. Interrupts KIN7

to KIN0 correspond to the IRQ6 interrupt. Interrupt request generation pin conditions, interrupt

request enabling, interrupt control level setting, and interrupt request status indications, are all in

accordance with the IRQ6 interrupt settings.

When pins KIN7 to KIN0 are used as key-sense interrupt input pins, either low-level sensing or

falling-edge sensing must be designated as the interrupt sense condition for the corresponding

interrupt source (IRQ6).

5.3.2

There are 38 sources for internal interrupts from on-chip supporting modules, plus one software

interrupt source (address break).

5.3.3

Table 5.4 shows interrupt exception handling sources, vector addresses, and interrupt priorities.

For default priorities, the lower the vector number, the higher the priority.

Priorities among modules can be set by means of ICR. The situation when two or more modules

are set to the same priority, and priorities within a module, are fixed as shown in table 5.4.

For each on-chip supporting module there are flags that indicate the interrupt request status,

and enable bits that select enabling or disabling of these interrupts. If any one of these is set to

1, an interrupt request is issued to the interrupt controller.

The interrupt control level can be set by means of ICR.

The DTC can be activated by an FRT, TMR, SCI, or other interrupt request. When the DTC is

activated by an interrupt, the interrupt control mode and interrupt mask bits have no effect.

Internal Interrupts

Interrupt Exception Vector Table

Rev. 4.00 Jun 06, 2006 page 115 of 1004

Section 5 Interrupt Controller

REJ09B0301-0400

Related parts for DF2134AFA20V

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: