DF2134AFA20V Renesas Electronics America, DF2134AFA20V Datasheet - Page 1020

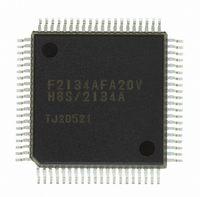

DF2134AFA20V

Manufacturer Part Number

DF2134AFA20V

Description

IC H8S/2100 MCU FLASH 80QFP

Manufacturer

Renesas Electronics America

Series

H8® H8S/2100r

Datasheets

1.HEWH8E10A.pdf

(19 pages)

2.D12312SVTE25V.pdf

(341 pages)

3.DF2134AFA20V.pdf

(1063 pages)

Specifications of DF2134AFA20V

Core Processor

H8S/2000

Core Size

16-Bit

Speed

20MHz

Connectivity

IrDA, SCI

Peripherals

POR, PWM, WDT

Number Of I /o

58

Program Memory Size

128KB (128K x 8)

Program Memory Type

FLASH

Ram Size

4K x 8

Voltage - Supply (vcc/vdd)

4 V ~ 5.5 V

Data Converters

A/D 8x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-20°C ~ 75°C

Package / Case

80-QFP

For Use With

3DK2166 - DEV EVAL KIT H8S/2166

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2134AFA20V

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 1020 of 1063

- Download datasheet (6Mb)

Appendix B Internal I/O Registers

SEDGR—Edge Sense Register

Rev. 4.00 Jun 06, 2006 page 964 of 1004

REJ09B0301-0400

Bit

Initial value

Read/Write

Notes: 1.

2.

Only 0 can be written, to clear the flags.

The initial value is undefined since it depends on the pin states.

VSYNCI edge

VEDG

R/(W)

0

1

7

0

[Clearing condition]

When 0 is written in VEDG after reading VEDG = 1

[Setting condition]

When a rising edge is detected on the VSYNCI pin

*

1

HEDG

HSYNCI edge

R/(W)

0

1

6

0

[Clearing condition]

When 0 is written in HEDG after reading HEDG = 1

When a rising edge is detected on the HSYNCI pin

[Setting condition]

*

1

CEDG

R/(W)

CSYNCI edge

0

1

5

0

[Clearing condition]

When 0 is written in CEDG after reading CEDG = 1

[Setting condition]

When a rising edge is detected on the CSYNCI pin

*

1

HFEDG

HFBACKI edge

R/(W)

0

1

4

0

[Clearing condition]

When 0 is written in HFEDG after reading HFEDG = 1

[Setting condition]

When a rising edge is detected on the HFBACKI pin

VFBACKI edge

*

0

1

1

VFEDG

[Clearing condition]

When 0 is written in VFEDG after reading VFEDG = 1

[Setting condition]

When a rising edge is detected on the VFBACKI pin

R/(W)

H'FFFF

3

0

*

1

Pre-equalization flag

0

1

PREQF

R/(W)

[Clearing condition]

When 0 is written in PREQF after

reading PREQF = 1

[Setting condition]

When an IHI signal 2fH modification

condition is detected

2

0

IHI signal level

*

0

1

1

IVI signal level

The IHI signal is low

The IHI signal is high

0

1

IHI

— *

R

1

The IVI signal is low

The IVI signal is high

Timer Connection

2

IVI

— *

R

0

2

Related parts for DF2134AFA20V

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: