DF2134AFA20V Renesas Electronics America, DF2134AFA20V Datasheet - Page 183

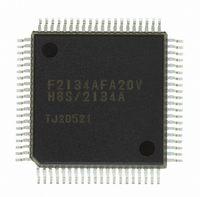

DF2134AFA20V

Manufacturer Part Number

DF2134AFA20V

Description

IC H8S/2100 MCU FLASH 80QFP

Manufacturer

Renesas Electronics America

Series

H8® H8S/2100r

Datasheets

1.HEWH8E10A.pdf

(19 pages)

2.D12312SVTE25V.pdf

(341 pages)

3.DF2134AFA20V.pdf

(1063 pages)

Specifications of DF2134AFA20V

Core Processor

H8S/2000

Core Size

16-Bit

Speed

20MHz

Connectivity

IrDA, SCI

Peripherals

POR, PWM, WDT

Number Of I /o

58

Program Memory Size

128KB (128K x 8)

Program Memory Type

FLASH

Ram Size

4K x 8

Voltage - Supply (vcc/vdd)

4 V ~ 5.5 V

Data Converters

A/D 8x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-20°C ~ 75°C

Package / Case

80-QFP

For Use With

3DK2166 - DEV EVAL KIT H8S/2166

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2134AFA20V

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 183 of 1063

- Download datasheet (6Mb)

Figure 5.10 shows a flowchart of the interrupt acceptance operation in this case.

1. If an interrupt source occurs when the corresponding interrupt enable bit is set to 1, an

2. When interrupt requests are sent to the interrupt controller, a control level 1 interrupt,

3. The I bit is then referenced. If the I bit is cleared to 0, the UI bit has no effect.

4. When an interrupt request is accepted, interrupt exception handling starts after execution of the

5. The PC and CCR are saved to the stack area by interrupt exception handling. The PC saved on

6. Next, the I and UI bits in CCR are set to 1. This disables all interrupts except NMI and address

7. A vector address is generated for the accepted interrupt, and execution of the interrupt

interrupt request is sent to the interrupt controller.

according to the control level set in ICR, has priority for selection, and other interrupt requests

are held pending. If a number of interrupt requests with the same control level setting are

generated at the same time, the interrupt request with the highest priority according to the

priority system shown in table 5.4 is selected.

An interrupt request set to interrupt control level 0 is accepted when the I bit is cleared to 0. If

the I bit is set to 1, only NMI and address break interrupts are accepted, and other interrupt

requests are held pending.

An interrupt request set to interrupt control level 1 has priority over an interrupt request set to

interrupt control level 0, and is accepted if the I bit is cleared to 0, or if the I bit is set to 1 and

the UI bit is cleared to 0.

When both the I bit and the UI bit are set to 1, only NMI and address break interrupts are

accepted, and other interrupt requests are held pending.

current instruction has been completed.

the stack shows the address of the first instruction to be executed after returning from the

interrupt handling routine.

break.

handling routine starts at the address indicated by the contents of that vector address.

Rev. 4.00 Jun 06, 2006 page 127 of 1004

Section 5 Interrupt Controller

REJ09B0301-0400

Related parts for DF2134AFA20V

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: