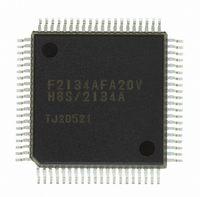

DF2134AFA20V Renesas Electronics America, DF2134AFA20V Datasheet

DF2134AFA20V

Specifications of DF2134AFA20V

Available stocks

Related parts for DF2134AFA20V

DF2134AFA20V Summary of contents

Page 1

To our customers, Old Company Name in Catalogs and Other Documents st On April 1 , 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the ...

Page 2

All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm ...

Page 3

H8S/2138 Group, H8S/2134 Group, H8S/2138F-ZTAT™, H8S/2134F-ZTAT™, 16 H8S/2132F-ZTAT™ Hardware Manual Renesas 16-Bit Single-Chip Microcomputer H8S Family/H8S/2100 Series H8S/2138 H8S/2137 The revision list can be viewed directly by clicking the title page. The revision list summarizes the locations of revisions and ...

Page 4

Keep safety first in your circuit designs! 1. Renesas Technology Corp. puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead ...

Page 5

General Precautions on Handling of Product 1. Treatment of NC Pins Note: Do not connect anything to the NC pins. The NC (not connected) pins are either not connected to any of the internal circuitry or are used as test ...

Page 6

Configuration of This Manual This manual comprises the following items: 1. General Precautions on Handling of Product 2. Configuration of This Manual 3. Preface 4. Main Revisions for This Edition The list of revisions is a summary of points that ...

Page 7

The H8S/2138 Group and H8S/2134 Group comprise high-performance microcomputers with a 32-bit H8S/2000 CPU core, and a set of on-chip supporting functions required for system configuration. The H8S/2000 CPU can execute basic instructions in one state, and is provided with ...

Page 8

On-Chip Supporting Modules Group Product names Bus controller (BSC) Data transfer controller (DTC) 8-bit PWM timer (PWM) 14-bit PWM timer (PWMX) 16-bit free-running timer (FRT) 8-bit timer (TMR) Timer connection Watchdog timer (WDT) Serial communication interface (SCI ...

Page 9

Main Revisions for This Edition Item Page All — 1.3.2 Pin Functions in 12 Each Operating Mode Table 1.2 H8S/2138 Group Pin Functions in Each Operating Mode 2.6.1 Overview 42 Table 2.1 Instruction Classification Revision (See Manual for Details) • ...

Page 10

Item Page 9.3.1 Correspondence 251 between PWM Data Register Contents and Output Waveform Table 9.4 Duty Cycle of Basic Pulse 10.1.3 Pin configuration 255 Table 10.1 Input and Output Pins 12.1 Overview 305 Rev. 4.00 Jun 06, 2006 page viii ...

Page 11

Item Page 16.4 Usage Notes 514 to 521 17.1.3 Input and Output 525 Pins Table 17.1 Host Interface Input/Output Pins 19.4.3 Input Sampling 566 and A/D Conversion Time Figure 19.5 A/D Conversion Timing 19.6 Usage Notes 572 Figure 19.11 Example ...

Page 12

Item Page 21.6.1 Boot Mode 597 Figure 21.10 RAM Areas in Boot Mode 598 22.4.5 Register 632 Configuration Table 22.4 Flash Memory Registers 23.7 Subclock Input 678 Circuit 24.1 Overview 682 Table 24.1 H8S/2138 Group and H8S/2134 Group Internal States ...

Page 13

Item Page 25.2.7 Usage Note 732 Figure 25.3 Connection of External Capacitor (Mask ROM Type Incorporating Step-Down Circuit and Product Not Incorporating Step-Down Circuit) 25.3.2 DC 735 Characteristics Table 25.16 DC Characteristics (1) 736 Table 25.16 DC 738 Characteristics (2) ...

Page 14

Item Page 25.3.2 DC 740 Characteristics Table 25.16 DC Characteristics (3) 742 25.3.6 Flash Memory 756 Characteristics Table 25.27 Flash Memory Characteristics (Programming/Erasing 757 Operating Range) 25.4.2 DC 761 Characteristics Table 25.29 DC Characteristics (1) Table 25.29 DC 766 Characteristics ...

Page 15

Item Page 25.5.6 Flash Memory 797 Characteristics Table 25.49 Flash Memory Characteristics (Programming/Erasing 798 Operating Range) B.3 Function 906 907 Revision (See Manual for Details) Table 25.49 amended Item Symbol Min Reprogramming count N WEC Data retention time * 10 ...

Page 16

Item Page B.3 Function 938 939 Rev. 4.00 Jun 06, 2006 page xiv of liv Revision (See Manual for Details) STCR H'FFC3 System Figure amended Bit — IICX1 IICX0 IICE Initial value Read/Write R/W ...

Page 17

Item Page B.3 Function 942 959 Revision (See Manual for Details) WSCR H'FFC7 Bus Controller Figure amended Bit 7 6 RAMS RAM0 Initial value 0 0 Read/Write R/W R/W Reserved Note: Always write 0 when writing to these bits in ...

Page 18

Item Page Appendix G Package 1002 Dimensions Figure G.1 Package Dimensions (FP-80A) Figure G.2 Package 1003 Dimensions (TFP-80C) Rev. 4.00 Jun 06, 2006 page xvi of liv Revision (See Manual for Details) Figure replaced Figure replaced ...

Page 19

Section 1 Overview ............................................................................................................. 1.1 Overview........................................................................................................................... 1.2 Internal Block Diagram..................................................................................................... 1.3 Pin Arrangement and Functions........................................................................................ 1.3.1 Pin Arrangement .................................................................................................. 1.3.2 Pin Functions in Each Operating Mode ............................................................... 11 1.3.3 Pin Functions ....................................................................................................... 18 Section 2 CPU ...................................................................................................................... 25 2.1 Overview........................................................................................................................... ...

Page 20

Bus-Released State............................................................................................... 65 2.8.6 Power-Down State ............................................................................................... 65 2.9 Basic Timing ..................................................................................................................... 66 2.9.1 Overview.............................................................................................................. 66 2.9.2 On-Chip Memory (ROM, RAM) ......................................................................... 66 2.9.3 On-Chip Supporting Module Access Timing ...................................................... 68 2.9.4 External Address Space Access Timing .............................................................. 69 ...

Page 21

Section 5 Interrupt Controller 5.1 Overview........................................................................................................................... 101 5.1.1 Features................................................................................................................ 101 5.1.2 Block Diagram ..................................................................................................... 102 5.1.3 Pin Configuration................................................................................................. 102 5.1.4 Register Configuration......................................................................................... 103 5.2 Register Descriptions ........................................................................................................ 104 5.2.1 System Control Register (SYSCR) ...................................................................... 104 5.2.2 Interrupt Control Registers A ...

Page 22

Features................................................................................................................ 137 6.1.2 Block Diagram ..................................................................................................... 138 6.1.3 Pin Configuration................................................................................................. 139 6.1.4 Register Configuration......................................................................................... 139 6.2 Register Descriptions ........................................................................................................ 140 6.2.1 Bus Control Register (BCR) ................................................................................ 140 6.2.2 Wait State Control Register (WSCR) .................................................................. 141 6.3 Overview of Bus ...

Page 23

DTC Transfer Count Register B (CRB)............................................................... 166 7.2.7 DTC Enable Registers (DTCER) ......................................................................... 166 7.2.8 DTC Vector Register (DTVECR)........................................................................ 167 7.2.9 Module Stop Control Register (MSTPCR) .......................................................... 168 7.3 Operation .......................................................................................................................... 169 7.3.1 Overview.............................................................................................................. 169 7.3.2 Activation Sources ............................................................................................... ...

Page 24

Port 5................................................................................................................................. 218 8.6.1 Overview.............................................................................................................. 218 8.6.2 Register Configuration......................................................................................... 218 8.6.3 Pin Functions ....................................................................................................... 220 8.7 Port 6................................................................................................................................. 221 8.7.1 Overview.............................................................................................................. 221 8.7.2 Register Configuration......................................................................................... 222 8.7.3 Pin Functions ....................................................................................................... 225 8.7.4 MOS Input Pull-Up Function............................................................................... 227 8.8 Port ...

Page 25

Correspondence between PWM Data Register Contents and Output Waveform.......................................................................................... 251 Section 10 14-Bit PWM D/A 10.1 Overview........................................................................................................................... 253 10.1.1 Features................................................................................................................ 253 10.1.2 Block Diagram ..................................................................................................... 254 10.1.3 Pin Configuration................................................................................................. 255 10.1.4 Register Configuration......................................................................................... 255 10.2 Register Descriptions ........................................................................................................ 256 ...

Page 26

Setting of FRC Overflow Flag (OVF) ................................................................. 294 11.3.8 Automatic Addition of OCRA and OCRAR/OCRAF ......................................... 294 11.3.9 ICRD and OCRDM Mask Signal Generation ...................................................... 295 11.4 Interrupts ........................................................................................................................... 296 11.5 Sample Application........................................................................................................... 297 11.6 Usage Notes ...................................................................................................................... 298 ...

Page 27

Contention between Compare-Matches A and B................................................. 338 12.6.5 Switching of Internal Clocks and TCNT Operation............................................. 338 Section 13 Timer Connection [H8S/2138 Group] 13.1 Overview........................................................................................................................... 341 13.1.1 Features................................................................................................................ 341 13.1.2 Block Diagram ..................................................................................................... 342 13.1.3 Input and Output Pins .......................................................................................... ...

Page 28

Timing of Setting of Overflow Flag (OVF) ......................................................... 383 14.4 Interrupts ........................................................................................................................... 384 14.5 Usage Notes ...................................................................................................................... 384 14.5.1 Contention between Timer Counter (TCNT) Write and Increment ..................... 384 14.5.2 Changing Value of CKS2 to CKS0...................................................................... 385 14.5.3 Switching ...

Page 29

Input/Output Pins ................................................................................................. 458 16.1.4 Register Configuration......................................................................................... 459 16.2 Register Descriptions ........................................................................................................ 460 2 16.2 Bus Data Register (ICDR) ............................................................................. 460 16.2.2 Slave Address Register (SAR) ............................................................................. 463 16.2.3 Second Slave Address Register (SARX) ............................................................. 464 2 ...

Page 30

Status Register 2 (STR2) ..................................................................................... 533 17.2.10 Module Stop Control Register (MSTPCR) .......................................................... 535 17.3 Operation .......................................................................................................................... 536 17.3.1 Host Interface Operation...................................................................................... 536 17.3.2 Control States....................................................................................................... 536 17.3.3 A20 Gate .............................................................................................................. 537 17.3.4 Host Interface Pin Shutdown Function ................................................................ ...

Page 31

External Trigger Input Timing............................................................................. 567 19.5 Interrupts ........................................................................................................................... 567 19.6 Usage Notes ...................................................................................................................... 568 Section 20 RAM .................................................................................................................. 573 20.1 Overview........................................................................................................................... 573 20.1.1 Block Diagram ..................................................................................................... 573 20.1.2 Register Configuration......................................................................................... 574 20.2 System Control Register (SYSCR) ................................................................................... 574 20.3 ...

Page 32

Hardware Protection ............................................................................................ 605 21.8.2 Software Protection.............................................................................................. 605 21.8.3 Error Protection.................................................................................................... 606 21.9 Interrupt Handling when Programming/Erasing Flash Memory....................................... 608 21.10 Flash Memory Programmer Mode .................................................................................... 609 21.10.1 Programmer Mode Setting ................................................................................... 609 21.10.2 Socket Adapters and Memory Map ...

Page 33

Program Mode ..................................................................................................... 646 22.7.2 Program-Verify Mode.......................................................................................... 647 22.7.3 Erase Mode .......................................................................................................... 649 22.7.4 Erase-Verify Mode .............................................................................................. 649 22.8 Flash Memory Protection.................................................................................................. 651 22.8.1 Hardware Protection ............................................................................................ 651 22.8.2 Software Protection.............................................................................................. 651 22.8.3 Error Protection.................................................................................................... 652 22.9 Interrupt Handling ...

Page 34

Section 24 Power-Down State 24.1 Overview........................................................................................................................... 681 24.1.1 Register Configuration......................................................................................... 685 24.2 Register Descriptions ........................................................................................................ 685 24.2.1 Standby Control Register (SBYCR) .................................................................... 685 24.2.2 Low-Power Control Register (LPWRCR) ........................................................... 687 24.2.3 Timer Control/Status Register (TCSR) ................................................................ 689 24.2.4 Module Stop ...

Page 35

DC Characteristics ............................................................................................... 707 25.2.3 AC Characteristics ............................................................................................... 718 25.2.4 A/D Conversion Characteristics........................................................................... 727 25.2.5 D/A Conversion Characteristics........................................................................... 729 25.2.6 Flash Memory Characteristics ............................................................................. 730 25.2.7 Usage Note........................................................................................................... 731 25.3 Electrical Characteristics of H8S/2138 F-ZTAT (A-Mask Version), and Mask ...

Page 36

A.2 Instruction Codes .............................................................................................................. 831 A.3 Operation Code Map......................................................................................................... 845 A.4 Number of States Required for Execution ........................................................................ 849 A.5 Bus States during Instruction Execution ........................................................................... 862 Appendix B Internal I/O Registers B.1 Addresses .......................................................................................................................... 878 B.2 Register Selection Conditions ...

Page 37

Section 1 Overview Figure 1.1 Internal Block Diagram of H8S/2138 Group..................................................... Figure 1.2 Internal Block Diagram of H8S/2134 Group..................................................... Figure 1.3 Pin Arrangement of H8S/2138 Group (FP-80A, TFP-80C: Top View) ............ Figure 1.4 Pin Arrangement of H8S/2134 Group (FP-80A, TFP-80C: ...

Page 38

Figure 4.2 Reset Sequence (Mode 3) .................................................................................. 95 Figure 4.3 Reset Sequence (Mode 1) .................................................................................. 96 Figure 4.4 Interrupt Sources and Number of Interrupts ...................................................... 97 Figure 4.5 (1) Stack Status after Exception Handling (Normal Mode) .................................... 99 Figure 4.5 ...

Page 39

Figure 7.4 Correspondence between DTC Vector Address and Register Information ....... 173 Figure 7.5 Location of DTC Register Information in Address Space................................. 175 Figure 7.6 Memory Mapping in Normal Mode .................................................................. 176 Figure 7.7 Memory Mapping in Repeat Mode.................................................................... 177 ...

Page 40

Figure 10.4 (3) Output Waveform.............................................................................................. 268 Figure 10.4 (4) Output Waveform.............................................................................................. 268 Section 11 16-Bit Free-Running Timer Figure 11.1 Block Diagram of 16-Bit Free-Running Timer ................................................. 270 Figure 11.2 Input Capture Buffering (Example)................................................................... 274 Figure 11.3 Increment Timing with Internal ...

Page 41

Figure 12.10 Timing of Input Capture Signal (When Input Capture Input Signal Enters while TICRR and TICRF Are Being Read)....................................................... 331 Figure 12.11 Switching of Input Capture Signal .................................................................... 331 Figure 12.12 Pulse Output (Example) .................................................................................... 334 Figure 12.13 Contention ...

Page 42

Figure 15.8 Example of SCI Operation in Reception (Example with 8-Bit Data, Parity, One Stop Bit) .............................................. 429 Figure 15.9 Example of Inter-Processor Communication Using Multiprocessor Format (Transmission of Data H'AA to Receiving Station A) ...................................... 431 Figure 15.10 Sample ...

Page 43

Figure 16.16 Flowchart for Slave Receive Mode (Example).................................................. 503 Figure 16.17 Flowchart for Slave Transmit Mode (Example) ................................................ 504 Figure 16.18 Points for Attention Concerning Reading of Master Receive Data ................... 511 Figure 16.19 Flowchart and Timing of Start Condition ...

Page 44

Section 21 ROM (Mask ROM Version, H8S/2138 F-ZTAT, H8S/2134 F-ZTAT, and H8S/2132 F-ZTAT) Figure 21.1 ROM Block Diagram (H8S/2138, H8S/2134)................................................... 577 Figure 21.2 Block Diagram of Flash Memory ...................................................................... 581 Figure 21.3 Flash Memory Mode Transitions....................................................................... 582 Figure 21.4 Boot ...

Page 45

Figure 22.12 Program/Program-Verify Flowchart.................................................................. 648 Figure 22.13 Erase/Erase-Verify Flowchart (Single-Block Erase) ......................................... 650 Figure 22.14 Flash Memory State Transitions........................................................................ 653 Figure 22.15 Memory Map in Programmer Mode.................................................................. 656 Figure 22.16 Memory Read Mode Timing Waveforms after Command Write...................... 658 Figure ...

Page 46

Figure 25.9 Interrupt Input Timing ....................................................................................... 802 Figure 25.10 Basic Bus Timing (Two-State Access).............................................................. 803 Figure 25.11 Basic Bus Timing (Three-State Access)............................................................ 804 Figure 25.12 Basic Bus Timing (Three-State Access with One Wait State)........................... 805 Figure 25.13 Burst ROM Access ...

Page 47

Figure C.18 Port 6 Block Diagram (Pin P64)........................................................................ 982 Figure C.19 Port 6 Block Diagram (Pin P66)........................................................................ 983 Figure C.20 Port 6 Block Diagram (Pin P67)........................................................................ 984 Figure C.21 Port 7 Block Diagram (Pins P70 to P75) ........................................................... 985 Figure ...

Page 48

Section 1 Overview Table 1.1 Overview ................................................................................................................ Table 1.2 H8S/2138 Group Pin Functions in Each Operating Mode ..................................... 11 Table 1.3 H8S/2134 Group Pin Functions in Each Operating Mode ..................................... 15 Table 1.4 Pin Functions.......................................................................................................... 18 Section 2 CPU Table ...

Page 49

Section 6 Bus Controller Table 6.1 Bus Controller Pins ................................................................................................ 139 Table 6.2 Bus Controller Registers ........................................................................................ 139 Table 6.3 Bus Specifications for Each Area (Basic Bus Interface) ........................................ 144 IOS Signal Output Range Settings ......................................................................... 145 Table 6.4 Table ...

Page 50

Section 9 8-Bit PWM Timers [H8S/2138 Group] Table 9.1 Pin Configuration ................................................................................................... 243 Table 9.2 PWM Timer Module Registers .............................................................................. 243 Table 9.3 Resolution, PWM Conversion Period, and Carrier Frequency when = 20 MHz.................................................................................................. 245 Table 9.4 Duty Cycle of ...

Page 51

Table 13.9 Meaning of HSYNCO Output in Each Mode......................................................... 367 Table 13.10 Meaning of VSYNCO Output in Each Mode......................................................... 368 Section 14 Watchdog Timer (WDT) Table 14.1 WDT Pin ................................................................................................................ 374 Table 14.2 WDT Registers....................................................................................................... 374 Section 15 Serial Communication ...

Page 52

Table 17.8 Fast A20 Gate Output Signals ................................................................................ 539 Table 17.9 Scope of HIF Pin Shutdown in Slave Mode........................................................... 540 Table 17.10 Input Buffer Full Interrupts .................................................................................... 541 Table 17.11 HIRQ Setting/Clearing Conditions......................................................................... 541 Section 18 D/A Converter Table 18.1 ...

Page 53

Table 21.20 Status Polling Output Truth Table.......................................................................... 620 Table 21.21 Command Wait State Transition Time Specifications ........................................... 620 Table 21.22 Registers Present in F-ZTAT Version but Absent in Mask ROM Version ............ 622 Section 22 ROM (H8S/2138 F-ZTAT A-Mask Version, ...

Page 54

Table 24.3 Power-Down State Registers.................................................................................. 685 Table 24.4 MSTP Bits and Corresponding On-Chip Supporting Modules .............................. 694 Table 24.5 Oscillation Settling Time Settings.......................................................................... 696 Section 25 Electrical Characteristics Table 25.1 Power Supply Voltage and Operating Range (1) (F-ZTAT Products) ................... ...

Page 55

Table 25.25 A/D Conversion Characteristics (CIN7 to CIN0 Input: 134/266-State Conversion) ................................................. 754 Table 25.26 D/A Conversion Characteristics ............................................................................. 755 Table 25.27 Flash Memory Characteristics (Programming/Erasing Operating Range) ............. 756 Table 25.28 Absolute Maximum Ratings................................................................................... 759 Table 25.29 DC Characteristics ...

Page 56

Table A.3 Operation Code Map (4) ........................................................................................ 848 Table A.4 Number of States per Cycle.................................................................................... 850 Table A.5 Number of Cycles per Instruction .......................................................................... 851 Table A.6 Instruction Execution Cycle ................................................................................... 864 Appendix D Pin States Table D.1 I/O Port ...

Page 57

Overview The H8S/2138 Group and H8S/2134 Group comprise microcomputers (MCUs) built around the H8S/2000 CPU, employing Renesas Technology proprietary architecture, and equipped with supporting modules on-chip. The H8S/2000 CPU has an internal 32-bit architecture, is provided with sixteen 16-bit ...

Page 58

Section 1 Overview Table 1.1 Overview Item Specifications CPU General-register architecture High-speed operation suitable for real-time control Instruction set suitable for high-speed operation Two CPU operating modes Operating modes Three MCU operating modes Mode Rev. 4.00 Jun ...

Page 59

Item Specifications Bus controller 2-state or 3-state access space can be designated for external expansion areas Number of program wait states can be set for external expansion areas Data transfer Can be activated by internal interrupt or software controller (DTC) ...

Page 60

Section 1 Overview Item Specifications 14-bit PWM timer outputs (PWMX) Resolution: 1/16384 312.5 kHz maximum carrier frequency (20-MHz operation) Serial communication Asynchronous mode or synchronous mode selectable interface Multiprocessor communication function (SCI: 2 channels, SCI0 and SCI1) ...

Page 61

Item Specifications Memory Flash memory or mask ROM High-speed static RAM Product Name H8S/2134, H8S/2138 H8S/2133 H8S/2132, H8S/2137 H8S/2130 Nine external interrupt pins (NMI, IRQ0 to IRQ7) Interrupt controller 39 internal interrupt sources Three priority levels settable Power-down state Medium-speed ...

Page 62

Section 1 Overview Item Specifications Product lineup (preliminary) Group H8S/2138 H8S/2134 Notes: 1. “W” indicates the I Rev. 4.00 Jun 06, 2006 page 6 of 1004 REJ09B0301-0400 Product Code * 3 Mask ROM F-ZTAT™ Versions Versions HD64F2138 * HD6432138S HD6432138SW ...

Page 63

Internal Block Diagram An internal block diagram of the H8S/2138 Group is shown in figure 1.1, and an internal block diagram of the H8S/2134 Group in figure 1.2. RES XTAL EXTAL MD1 MD0 NMI STBY P97/WAIT/SDA0 P96/ /EXCL P95/AS/IOS/CS1 ...

Page 64

Section 1 Overview RES XTAL EXTAL MD1 MD0 NMI STBY P97/WAIT P96/ /EXCL P95/AS/IOS P94/WR P93/RD P92/IRQ0 P91/IRQ1 P90/IRQ2/ADTRG P67/CIN7/KIN7/IRQ7 P66/FTOB/CIN6/KIN6/IRQ6 P65/FTID/CIN5/KIN5 P64/FTIC/CIN4/KIN4 P63/FTIB/CIN3/KIN3 P62/FTIA/CIN2/KIN2/TMIY P61/FTOA/CIN1/KIN1 P60/FTCI/CIN0/KIN0 P47/PWX1 P46/PWX0 P45/TMRI1 P44/TMO1 P43/TMCI1 P42/TMRI0/SCK2 P41/TMO0/RxD2/IrRxD P40/TMCI0/TxD2/IrTxD P52/SCK0 P51/RxD0 P50/TxD0 Figure 1.2 ...

Page 65

Pin Arrangement and Functions 1.3.1 Pin Arrangement The pin arrangement of the H8S/2138 Group is shown in figure 1.3, and the pin arrangement of the H8S/2134 Group in figure 1. ...

Page 66

Section 1 Overview A3/P13 61 A2/P12 62 A1/P11 63 A0/P10 64 D0/P30 65 D1/P31 66 D2/P32 67 D3/P33 68 D4/P34 ...

Page 67

Pin Functions in Each Operating Mode Tables 1.2 and 1.3 show the pin functions of the H8S/2138 Group and H8S/2134 Group in each of the operating modes. Table 1.2 H8S/2138 Group Pin Functions in Each Operating Mode Pin No. ...

Page 68

Section 1 Overview Pin No. Expanded Modes FP-80A TFP-80C Mode 1 23 P62/FTIA/CIN2/ KIN2/TMIY/ VSYNCI 24 P63/FTIB/CIN3/ KIN3/VFBACKI 25 P64/FTIC/CIN4/ KIN4/CLAMPO 26 P65/FTID/CIN5/ KIN5 27 P66/FTOB/CIN6/ KIN6/IRQ6 28 P67/TMOX/CIN7/ KIN7/IRQ7 29 AVCC 30 P70/AN0 31 P71/AN1 32 P72/AN2 33 P73/AN3 ...

Page 69

Pin No. Expanded Modes FP-80A TFP-80C Mode 1 45 P46/PWX0 46 P47/PWX1 47 VCC1 48 A15 49 A14 50 A13 51 A12 52 A11 53 A10 VSS ...

Page 70

Section 1 Overview Pin No. Expanded Modes FP-80A TFP-80C Mode 1 75 P81 76 P82 77 P83 78 P84/IRQ3/TxD1 79 P85/IRQ4/RxD1 80 P86/IRQ5/SCK1/ SCL1 Rev. 4.00 Jun 06, 2006 page 14 of 1004 REJ09B0301-0400 Pin Name Single-Chip Modes Mode 2 ...

Page 71

Table 1.3 H8S/2134 Group Pin Functions in Each Operating Mode Pin No. Expanded Modes FP-80A TFP-80C Mode 1 RES 1 2 XTAL 3 EXTAL 4 MD1 5 MD0 6 NMI STBY 7 8 VCC2 (VCL) 9 P52/SCK0 10 P51/RxD0 11 ...

Page 72

Section 1 Overview Pin No. Expanded Modes FP-80A TFP-80C Mode 1 26 P65/FTID/CIN5/ KIN5 27 P66/FTOB/CIN6/ KIN6/IRQ6 28 P67/CIN7/KIN7/ IRQ7 29 AVCC 30 P70/AN0 31 P71/AN1 32 P72/AN2 33 P73/AN3 34 P74/AN4 35 P75/AN5 36 P76/AN6/DA0 37 P77/AN7/DA1 38 AVSS ...

Page 73

Pin No. Expanded Modes FP-80A TFP-80C Mode 1 53 A10 VSS ...

Page 74

Section 1 Overview 1.3.3 Pin Functions Table 1.4 summarizes the functions of the H8S/2138 Group and H8S/2134 Group pins. Table 1.4 Pin Functions Pin No. FP-80A Type Symbol TFP-80C Power VCC1, supply VCC2 8 * VCL ...

Page 75

Pin No. FP-80A Type Symbol TFP-80C Operating MD1 4 mode MD0 5 control RES System 1 control STBY 7 Address A15 55, bus Data bus WAIT Bus ...

Page 76

Section 1 Overview Pin No. FP-80A Type Symbol TFP-80C Interrupt NMI 6 signals IRQ0 20, IRQ7 78 to 80, 27, 28 16-bit free- FTCI 21 running timer (FRT) FTOA 22 FTOB 27 FTIA 23 FTIB 24 FTIC ...

Page 77

Pin No. FP-80A Type Symbol TFP-80C Serial com- TxD0 11 munication TxD1 78 interface TxD2 39 (SCI0, SCI1, RxD0 10 SCI2) RxD1 79 RxD2 40 SCK0 9 SCK1 80 SCK2 41 SCI with IrTxD 39 IrDA (SCI2) IrRxD 40 Host ...

Page 78

Section 1 Overview Pin No. FP-80A Type Symbol TFP-80C A/D AN7 converter AN0 (ADC) CN0 24, CN7 ADTRG 20 D/A DA0 36 converter DA1 37 (DAC) A/D AVCC 29 converter ...

Page 79

Pin No. FP-80A Type Symbol TFP-80C I/O ports P17 P10 P27 P20 P37 P30 P47 P40 P52 P50 P67 to ...

Page 80

Section 1 Overview Rev. 4.00 Jun 06, 2006 page 24 of 1004 REJ09B0301-0400 ...

Page 81

Overview The H8S/2000 CPU is a high-speed central processing unit with an internal 32-bit architecture that is upward-compatible with the H8/300 and H8/300H CPUs. The H8S/2000 CPU has sixteen 16-bit general registers, can address a 16-Mbyte (architecturally 4-Gbyte) linear ...

Page 82

Section 2 CPU High-speed operation All frequently-used instructions execute in one or two states Maximum clock rate: 8/16/32-bit register-register add/subtract 8-bit register-register multiply: 16 ÷ 8-bit register-register divide: 16 16-bit register-register multiply: 32 ÷ 16-bit register-register divide: ...

Page 83

Differences from H8/300 CPU In comparison to the H8/300 CPU, the H8S/2000 CPU has the following enhancements. More general registers and control registers Eight 16-bit extended registers, and one 8-bit control register, have been added. Expanded address space Normal ...

Page 84

Section 2 CPU 2.2 CPU Operating Modes The H8S/2000 CPU has two operating modes: normal and advanced. Normal mode supports a maximum 64-kbyte address space. Advanced mode supports a maximum 16-Mbyte total address space (architecturally the maximum total address space ...

Page 85

Exception Vector Table and Memory Indirect Branch Addresses: In normal mode the top area starting at H'0000 is allocated to the exception vector table. One branch address is stored per 16 bits. The configuration of the exception vector table in ...

Page 86

Section 2 CPU Stack Structure: When the program counter (PC) is pushed onto the stack in a subroutine call, and the PC and condition-code register (CCR) are pushed onto the stack in exception handling, they are stored as shown in ...

Page 87

Exception Vector Table and Memory Indirect Branch Addresses: In advanced mode the top area starting at H'00000000 is allocated to the exception vector table in units of 32 bits. In each 32 bits, the upper 8 bits are ignored and ...

Page 88

Section 2 CPU Stack Structure: In advanced mode, when the program counter (PC) is pushed onto the stack in a subroutine call, and the PC and condition-code register (CCR) are pushed onto the stack in exception handling, they are stored ...

Page 89

Address Space Figure 2.6 shows a memory map of the H8S/2000 CPU. The H8S/2000 CPU provides linear access to a maximum 64-kbyte address space in normal mode, and a maximum 16-Mbyte (architecturally 4-Gbyte) address space in advanced mode. H'0000 ...

Page 90

Section 2 CPU 2.4 Register Configuration 2.4.1 Overview The CPU has the internal registers shown in figure 2.7. There are two types of registers: general registers and control registers. General Registers (Rn) and Extended Registers (En) 15 ER0 ER1 ER2 ...

Page 91

General Registers The CPU has eight 32-bit general registers. These general registers are all functionally alike and can be used as both address registers and data registers. When a general register is used as a data register, it can ...

Page 92

Section 2 CPU SP (ER7) 2.4.3 Control Registers The control registers are the 24-bit program counter (PC), 8-bit extended control register (EXR), and 8-bit condition-code register (CCR). (1) Program Counter (PC) This 24-bit counter indicates the address of the next ...

Page 93

Condition-Code Register (CCR) This 8-bit register contains internal CPU status information, including an interrupt mask bit (I) and half-carry (H), negative (N), zero (Z), overflow (V), and carry (C) flags. Bit 7—Interrupt Mask Bit (I): Masks interrupts other than ...

Page 94

Section 2 CPU Operations can be performed on the CCR bits by the LDC, STC, ANDC, ORC, and XORC instructions. The and C flags are used as branching conditions for conditional branch (Bcc) instructions. 2.4.4 Initial Register ...

Page 95

Data Formats The CPU can process 1-bit, 4-bit (BCD), 8-bit (byte), 16-bit (word), and 32-bit (longword) data. Bit-manipulation instructions operate on 1-bit data by accessing bit … byte operand data. The ...

Page 96

Section 2 CPU Data Type General Register Word data Rn Word data En 15 MSB Longword data ERn 31 MSB En Legend: ERn: General register ER En: General register E Rn: General register R RnH: General register RH RnL: General ...

Page 97

Memory Data Formats Figure 2.11 shows the data formats in memory. The CPU can access word data and longword data in memory, but word or longword data must begin at an even address attempt is made to ...

Page 98

Section 2 CPU 2.6 Instruction Set 2.6.1 Overview The H8S/2000 CPU has 65 types of instructions. The instructions are classified by function in table 2.1. Table 2.1 Instruction Classification Function Instructions Data transfer MOV POP * , PUSH * 1 ...

Page 99

Instructions and Addressing Modes Table 2.2 indicates the combinations of instructions and addressing modes that the H8S/2000 CPU can use. Table 2.2 Combinations of Instructions and Addressing Modes Function Instruction Data MOV BWL BWL BWL BWL BWL BWL transfer ...

Page 100

Section 2 CPU 2.6.3 Table of Instructions Classified by Function Table 2.3 summarizes the instructions in each functional category. The notation used in table 2.3 is defined below. Operation Notation General register (destination General register (source ...

Page 101

Table 2.3 Instructions Classified by Function Type Instruction Data transfer MOV MOVFPE MOVTPE POP PUSH LDM * 3 STM * 3 Size * 1 Function B/W/L (EAs) Rd, Rs Moves data between two general registers or between a general register ...

Page 102

Section 2 CPU Type Instruction Arithmetic ADD operations SUB ADDX SUBX INC DEC ADDS SUBS DAA DAS MULXU MULXS DIVXU Rev. 4.00 Jun 06, 2006 page 46 of 1004 REJ09B0301-0400 Size * 1 Function B/W/L Rd ± Rs Rd, Rd ...

Page 103

Type Instruction Arithmetic DIVXS operations CMP NEG EXTU EXTS TAS Size * 1 Function B/W Rd ÷ Performs signed division on data in two general registers: either 16 bits ÷ 8 bits remainder or 32 bits ÷ 16 ...

Page 104

Section 2 CPU Type Instruction Logic AND operations OR XOR NOT Shift SHAL operations SHAR SHLL SHLR ROTL ROTR ROTXL ROTXR Rev. 4.00 Jun 06, 2006 page 48 of 1004 REJ09B0301-0400 Size * 1 Function B/W Rd, Rd ...

Page 105

Type Instruction Bit- BSET manipulation instructions BCLR BNOT BTST BAND BIAND BOR BIOR Size * 1 Function B 1 (<bit-No.> of <EAd>) Sets a specified bit in a general register or memory operand to 1. The bit number is specified ...

Page 106

Section 2 CPU Type Instruction Bit- BXOR manipulation instructions BIXOR BLD BILD BST BIST Rev. 4.00 Jun 06, 2006 page 50 of 1004 REJ09B0301-0400 Size * 1 Function B C (<bit-No.> of <EAd>) Exclusive-ORs the carry flag with a specified ...

Page 107

Type Instruction Branch Bcc instructions JMP BSR JSR RTS Size * 1 Function — Branches to a specified address if a specified condition is true. The branching conditions are listed below. Mnemonic Description BRA(BT) Always (true) BRN(BF) Never (false) BHI ...

Page 108

Section 2 CPU Type Instruction System TRAPA control RTE instructions SLEEP LDC STC ANDC ORC XORC NOP Rev. 4.00 Jun 06, 2006 page 52 of 1004 REJ09B0301-0400 Size * 1 Function — Starts trap-instruction exception handling. — Returns from an ...

Page 109

Type Instruction Block data EEPMOV.B transfer instructions EEPMOV.W Notes: 1. Size refers to the operand size. B: Byte W: Word L: Longword 2. Only register ER0, ER1, ER4, or ER5 should be used when using the TAS instruction. 3. Only ...

Page 110

Section 2 CPU Figure 2.12 shows examples of instruction formats. (1) Operation field only (2) Operation field and register fields op (3) Operation field, register fields, and effective address extension op (4) Operation field, effective address extension, and condition field ...

Page 111

Addressing Modes and Effective Address Calculation 2.7.1 Addressing Mode The CPU supports the eight addressing modes listed in table 2.4. Each instruction uses a subset of these addressing modes. Arithmetic and logic instructions can use the register direct and ...

Page 112

Section 2 CPU Register Indirect with Post-Increment or Pre-Decrement—@ERn+ or @-ERn: Register indirect with post-increment—@ERn+ The register field of the instruction code specifies an address register (ERn) which contains the address of a memory operand. After the operand is accessed, ...

Page 113

Immediate—#xx:8, #xx:16, or #xx:32: The instruction contains 8-bit (#xx:8), 16-bit (#xx:16), or 32-bit (#xx:32) immediate data as an operand. The ADDS, SUBS, INC, and DEC instructions contain immediate data implicitly. Some bit manipulation instructions contain 3-bit immediate data in the ...

Page 114

Section 2 CPU If an odd address is specified in word or longword memory access branch address, the least significant bit is regarded as 0, causing data to be accessed or an instruction code to be fetched ...

Page 115

Table 2.6 Effective Address Calculation Addressing Mode and No. Instruction Format 1 Register direct (Rn Register indirect (@ERn Register indirect with displacement @(d:16, ERn) or @(d:32, ERn disp 4 Register indirect ...

Page 116

Section 2 CPU Addressing Mode and No. Instruction Format 5 Absolute address @aa:8 op abs @aa:16 op abs @aa:24 op abs @aa:32 op abs 6 Immediate #xx:8/#xx:16/#xx:32 op IMM 7 Program-counter relative @(d:8, PC)/@(d:16, PC) op disp Rev. 4.00 Jun ...

Page 117

Addressing Mode and No. Instruction Format 8 Memory indirect @@aa:8 Normal mode op abs Advanced mode op abs Effective Address Calculation H'000000 abs Memory contents abs H'000000 31 ...

Page 118

Section 2 CPU 2.8 Processing States 2.8.1 Overview The CPU has five main processing states: the reset state, exception-handling state, program execution state, bus-released state, and power-down state. Figure 2.14 shows a diagram of the processing states. Figure 2.15 indicates ...

Page 119

End of bus request Bus-released state End of exception handling Exception-handling state RES = high Reset state * 1 From any state except hardware standby mode, a transition to the reset state occurs whenever RES Notes: 1. goes low. A ...

Page 120

Section 2 CPU 2.8.3 Exception-Handling State The exception-handling state is a transient state that occurs when the CPU alters the normal processing flow due to a reset, interrupt, or trap instruction. The CPU fetches a start address (vector) from the ...

Page 121

Figure 2.16 shows the stack after exception handling ends. Normal mode SP CCR CCR * PC (16 bits) Note: * Ignored when returning. Figure 2.16 Stack Structure after Exception Handling (Examples) 2.8.4 Program Execution State In this state the CPU ...

Page 122

Section 2 CPU stop mode permits halting of the operation of individual modules, other than the CPU. Subactive mode, subsleep mode, and watch mode are power-down modes that use subclock input. For details, refer to section 24, Power-Down State. Sleep ...

Page 123

Internal address bus Internal read signal Read access Internal data bus Internal write signal Write access Internal data bus Figure 2.17 On-Chip Memory Access Cycle Address bus Data bus Figure 2.18 Pin States during On-Chip Memory Access ...

Page 124

Section 2 CPU 2.9.3 On-Chip Supporting Module Access Timing The on-chip supporting modules are accessed in two states. The data bus is either 8 bits or 16 bits wide, depending on the particular internal I/O register being accessed. Figure 2.19 ...

Page 125

Address bus Data bus Figure 2.20 Pin States during On-Chip Supporting Module Access 2.9.4 External Address Space Access Timing The external address space is accessed with an 8-bit data bus width in a two-state or three-state bus ...

Page 126

Section 2 CPU 2.10 Usage Note 2.10.1 TAS Instruction Only register ER0, ER1, ER4, or ER5 should be used when using the TAS instruction. The TAS instruction is not generated by the Renesas H8S and H8/300 series C/C++ compilers. If ...

Page 127

Section 3 MCU Operating Modes 3.1 Overview 3.1.1 Operating Mode Selection The H8S/2138 Group and H8S/2134 Group have three operating modes (modes 1 to 3). These modes enable selection of the CPU operating mode and enabling/disabling of on-chip ROM, by ...

Page 128

Section 3 MCU Operating Modes 3.1.2 Register Configuration The H8S/2138 Group and H8S/2134 Group have a mode control register (MDCR) that indicates the inputs at the mode pins (MD1 and MD0), a system control register (SYSCR) and bus control register ...

Page 129

Bit 7—Expanded Mode Enable (EXPE): Sets expanded mode. In mode 1, this bit is fixed at 1 and cannot be modified. In modes 2 and 3, this bit has an initial value of 0, and can be read and written. ...

Page 130

Section 3 MCU Operating Modes Bit 6—IOS Enable (IOSE): Controls the function of the AS/IOS pin in expanded mode. Bit 6 IOSE Description The AS/IOS pin functions as the address strobe pin (AS) 0 (Low output when accessing an external ...

Page 131

Bit 0—RAM Enable (RAME): Enables or disables the on-chip RAM. The RAME bit is initialized when the reset state is released not initialized in software standby mode. Bit 0 RAME Description 0 On-chip RAM is disabled 1 On-chip ...

Page 132

Section 3 MCU Operating Modes 3.2.4 Serial Timer Control Register (STCR) Bit 7 — IICX1 Initial value 0 Read/Write R/W R/W STCR is an 8-bit readable/writable register that controls register access, the IIC operating mode (when the on-chip IIC option ...

Page 133

Bit 4 IICE Description 0 Addresses H'(FF)FF88 and H'(FF)FF89, and H'(FF)FF8E and H'(FF)FF8F, are used for SCI1 control register access Addresses H'(FF)FFA0 and H'(FF)FFA1, and H'(FF)FFA6 and H'(FF)FFA7, are used for SCI2 control register access Addresses H'(FF)FFD8 and H'(FF)FFD9, and ...

Page 134

Section 3 MCU Operating Modes 3.3 Operating Mode Descriptions 3.3.1 Mode 1 The CPU can access a 64-kbyte address space in normal mode. The on-chip ROM is disabled. Ports 1 and 2 function as an address bus, port 3 function ...

Page 135

Pin Functions in Each Operating Mode The pin functions of ports and 9 vary depending on the operating mode. Table 3.3 shows their functions in each operating mode. Table 3.3 Pin Functions in Each Mode Port ...

Page 136

Section 3 MCU Operating Modes Mode 1 (normal expanded mode with on-chip ROM disabled) H'0000 External address space H'E080 On-chip RAM * H'EFFF External address space H'FE50 Internal I/O registers 2 H'FEFF H'FF00 On-chip RAM (128 bytes) * H'FF7F H'FF80 ...

Page 137

Mode 2/EXPE = 1 (advanced expanded mode with on-chip ROM enabled) H'000000 H'01FFFF H'020000 External address H'FFE080 On-chip RAM H'FFEFFF External address H'FFFE50 Internal I/O registers 2 H'FFFEFF H'FFFF00 H'FFFF7F H'FFFF80 Internal I/O registers 1 H'FFFFFF Notes: 1. External addresses ...

Page 138

Section 3 MCU Operating Modes Mode 1 (normal expanded mode with on-chip ROM disabled) H'0000 External address space H'E080 On-chip RAM * H'EFFF External address space H'F800 Reserved area H'FE4F H'FE50 Internal I/O registers 2 H'FEFF H'FF00 On-chip RAM (128 ...

Page 139

Mode 2/EXPE = 1 (advanced expanded mode with on-chip ROM enabled) H'000000 H'01FFFF H'020000 External address H'FFE080 On-chip RAM H'FFEFFF External address H'FFF800 H'FFFE4F H'FFFE50 Internal I/O registers 2 H'FFFEFF H'FFFF00 H'FFFF7F H'FFFF80 Internal I/O registers 1 H'FFFFFF Notes: 1. ...

Page 140

Section 3 MCU Operating Modes Mode 1 (normal expanded mode with on-chip ROM disabled) H'0000 External address space H'E080 On-chip RAM * H'EFFF External address space H'FE50 Internal I/O registers 2 H'FEFF H'FF00 On-chip RAM (128 bytes) * H'FF7F H'FF80 ...

Page 141

Mode 2/EXPE = 1 (advanced expanded mode with on-chip ROM enabled) H'000000 On-chip ROM H'017FFF Reserved area H'01FFFF H'020000 External address H'FFE080 On-chip RAM H'FFEFFF External address H'FFFE50 Internal I/O registers 2 H'FFFEFF H'FFFF00 H'FFFF7F H'FFFF80 Internal I/O registers 1 ...

Page 142

Section 3 MCU Operating Modes Mode 1 (normal expanded mode with on-chip ROM disabled) H'0000 External address space H'E080 Reserved area * H'E880 On-chip RAM * H'EFFF External address space H'FE50 Internal I/O registers 2 H'FEFF H'FF00 On-chip RAM (128 ...

Page 143

Mode 2/EXPE = 1 (advanced expanded mode with on-chip ROM enabled) H'000000 On-chip ROM H'00FFFF Reserved area H'01FFFF H'020000 External address H'FFE080 Reserved area H'FFE880 On-chip RAM H'FFEFFF External address H'FFFE50 Internal I/O registers 2 H'FFFEFF H'FFFF00 On-chip RAM H'FFFF7F ...

Page 144

Section 3 MCU Operating Modes Mode 1 (normal expanded mode with on-chip ROM disabled) H'0000 External address space H'E080 Reserved area * H'E880 On-chip RAM * H'EFFF External address space H'FE50 Internal I/O registers 2 H'FEFF H'FF00 On-chip RAM (128 ...

Page 145

Mode 2/EXPE = 1 (advanced expanded mode with on-chip ROM enabled) H'000000 On-chip ROM H'007FFF Reserved area H'01FFFF H'020000 External address H'FFE080 Reserved area H'FFE880 On-chip RAM H'FFEFFF External address H'FFFE50 Internal I/O registers 2 H'FFFEFF H'FFFF00 H'FFFF7F H'FFFF80 Internal ...

Page 146

Section 3 MCU Operating Modes Rev. 4.00 Jun 06, 2006 page 90 of 1004 REJ09B0301-0400 ...

Page 147

Section 4 Exception Handling 4.1 Overview 4.1.1 Exception Handling Types and Priority As table 4.1 indicates, exception handling may be caused by a reset, direct transition, trap instruction, or interrupt. Exception handling is prioritized as shown in table 4.1. If ...

Page 148

Section 4 Exception Handling 4.1.2 Exception Handling Operation Exceptions originate from various sources. Trap instructions and interrupts are handled as follows: 1. The program counter (PC) and condition-code register (CCR) are pushed onto the stack. 2. The interrupt mask bits ...

Page 149

Table 4.2 Exception Vector Table Exception Source Reset Reserved for system use Direct transition External interrupt NMI Trap instruction (4 sources) Reserved for system use External interrupt IRQ0 IRQ1 IRQ2 IRQ3 IRQ4 IRQ5 IRQ6 IRQ7 Internal interrupt * 2 Notes: ...

Page 150

Section 4 Exception Handling 4.2 Reset 4.2.1 Overview A reset has the highest exception priority. When the RES pin goes low, all processing halts and the MCU enters the reset state. A reset initializes the internal state of the CPU ...

Page 151

RES Internal address bus Internal read signal Internal write signal Internal data bus (1) Reset exception vector address ((1) = H'0000) (2) Start address (contents of reset exception vector address) (3) Start address ((3) = (2)) (4) First program instruction ...

Page 152

Section 4 Exception Handling RES Address bus (1) (3) Reset exception vector address ((1) = H'0000, (3) = H'0001) (2) (4) Start address (contents of reset exception vector address) (5) Start address ((5) = (2) ...

Page 153

Interrupts Interrupt exception handling can be requested by nine external sources (NMI and IRQ7 to IRQ0) from 17 input pins (NMI, IRQ7 to IRQ0, and KIN7 to KIN0), and internal sources in the on-chip supporting modules. Figure 4.4 shows ...

Page 154

Section 4 Exception Handling 4.4 Trap Instruction Trap instruction exception handling starts when a TRAPA instruction is executed. Trap instruction exception handling can be executed at all times in the program execution state. The TRAPA instruction fetches a start address ...

Page 155

Stack Status after Exception Handling Figure 4.5 shows the stack after completion of trap instruction exception handling and interrupt exception handling. SP Note: * Ignored on return. Figure 4.5 (1) Stack Status after Exception Handling (Normal Mode) SP Note: ...

Page 156

Section 4 Exception Handling 4.6 Notes on Use of the Stack When accessing word data or longword data, the H8S/2138 Group or H8S/2134 Group chip assumes that the lowest address bit is 0. The stack should always be accessed by ...

Page 157

Section 5 Interrupt Controller 5.1 Overview 5.1.1 Features H8S/2138 Group and H8S/2134 Group MCUs control interrupts by means of an interrupt controller. The interrupt controller has the following features: Two interrupt control modes Either of two interrupt control modes can ...

Page 158

Section 5 Interrupt Controller 5.1.2 Block Diagram A block diagram of the interrupt controller is shown in figure 5.1. INTM1 INTM0 SYSCR NMIEG NMI input IRQ input Internal interrupt requests SWDTEND to IICI1 Interrupt controller Legend: IRQ sense control register ...

Page 159

Register Configuration Table 5.2 summarizes the registers of the interrupt controller. Table 5.2 Interrupt Controller Registers Name System control register IRQ sense control register H IRQ sense control register L IRQ enable register IRQ status register Keyboard matrix interrupt ...

Page 160

Section 5 Interrupt Controller 5.2 Register Descriptions 5.2.1 System Control Register (SYSCR) Bit 7 6 CS2E IOSE Initial value 0 0 Read/Write R/W R/W SYSCR is an 8-bit readable/writable register of which bits 5, 4, and 2 select the interrupt ...

Page 161

Interrupt Control Registers (ICRA to ICRC) Bit 7 ICR7 ICR6 Initial value 0 Read/Write R/W R/W The ICR registers are three 8-bit readable/writable registers that set the interrupt control level for interrupts other than NMI and ...

Page 162

Section 5 Interrupt Controller 5.2.3 IRQ Enable Register (IER) Bit 7 IRQ7E IRQ6E Initial value 0 Read/Write R/W R/W IER is an 8-bit readable/writable register that controls enabling and disabling of interrupt requests IRQ7 to IRQ0. IER is initialized to ...

Page 163

ISCRH and ISCRL are 8-bit readable/writable registers that select rising edge, falling edge, or both edge detection, or level sensing, for the input at pins IRQ7 to IRQ0. Each of the ISCR registers is initialized to H' reset ...

Page 164

Section 5 Interrupt Controller Bit n IRQnF Description 0 [Clearing conditions] Cleared by reading IRQnF when set to 1, then writing 0 in IRQnF When interrupt exception handling is executed when low-level detection is set (IRQnSCB = IRQnSCA = 0) ...

Page 165

Keyboard Matrix Interrupt Mask Register (KMIMR) 7 Bit KMIMR7 KMIMR6 Initial value 1 Read/Write R/W R/W KMIMR is an 8-bit readable/writable register that performs mask control for the keyboard matrix interrupt inputs (pins KIN7 to KIN0) and IRQ6 pin. ...

Page 166

Section 5 Interrupt Controller KMIMR0 (initial value 1) P60/KIN0 KMIMR5 (initial value 1) P65/KIN5 KMIMR6 (initial value 0) P66/KIN6/IRQ6 KMIMR7 (initial value 1) P67/KIN7/IRQ7 Figure 5.2 Relationship between Interrupts IRQ6, Interrupts KIN7 to KIN0, When pins KIN7 to KIN0 are ...

Page 167

Address Break Control Register (ABRKCR) Bit 7 CMF Initial value 0 Read/Write R ABRKCR is an 8-bit readable/writable register that performs address break control. ABRKCR is initialized to H' reset and in hardware standby mode ...

Page 168

Section 5 Interrupt Controller 5.2.8 Break Address Registers (BARA, BARB, BARC) Bit 7 BARA A23 A22 Initial value 0 Read/Write R/W R/W Bit 7 BARB A15 A14 Initial value 0 Read/Write R/W R/W Bit 7 BARC A7 ...

Page 169

Interrupt Sources Interrupt sources comprise external interrupts (NMI and IRQ7 to IRQ0) and internal interrupts. 5.3.1 External Interrupts There are nine external interrupt sources from 17 input pins (15 actual pins): NMI, IRQ7 to IRQ0, and KIN7 to KIN0. ...

Page 170

Section 5 Interrupt Controller IRQnSCA, IRQnSCB Edge/level detection circuit IRQn input Note Figure 5.3 Block Diagram of Interrupts IRQ7 to IRQ0 Figure 5.4 shows the timing of IRQnF setting. IRQn input pin IRQnF Figure 5.4 Timing ...

Page 171

Interrupts KIN7 to KIN0: Interrupts KIN7 to KIN0 are requested by input signals at pins KIN7 to KIN0. When any of pins KIN7 to KIN0 are used as key-sense inputs, the corresponding KMIMR bits should be cleared ...

Page 172

Section 5 Interrupt Controller Table 5.4 Interrupt Sources, Vector Addresses, and Interrupt Priorities Interrupt Source NMI IRQ0 IRQ1 IRQ2 IRQ3 IRQ4 IRQ5 IRQ6, KIN7 to KIN0 IRQ7 SWDTEND (software activation interrupt end) WOVI0 (interval timer) WOVI1 (interval timer) Address break ...

Page 173

Interrupt Source CMIA0 (compare-match A) CMIB0 (compare-match B) OVI0 (overflow) Reserved CMIA1 (compare-match A) CMIB1 (compare-match B) OVI1 (overflow) Reserved CMIAY (compare-match A) CMIBY (compare-match B) OVIY (overflow) ICIX (input capture X) IBF1 (IDR1 reception completed) IBF2 (IDR2 reception completed) ...

Page 174

Section 5 Interrupt Controller 5.4 Address Breaks 5.4.1 Features With the H8S/2138 Group and H8S/2134 Group possible to identify the prefetch of a specific address by the CPU and generate an address break interrupt, using the ABRKCR and ...

Page 175

Operation ABRKCR and BAR settings can be made so that an address break interrupt is generated when the CPU prefetches the address set in BAR. This address break function issues an interrupt request to the interrupt controller when the ...

Page 176

Section 5 Interrupt Controller • Program area in on-chip memory, 1-state execution instruction at specified break address Instruction Instruction fetch fetch Address bus H'0310 H'0312 NOP execution Break request signal H'0310 NOP H'0312 NOP H'0314 NOP H'0316 NOP • Program ...

Page 177

Interrupt Operation 5.5.1 Interrupt Control Modes and Interrupt Operation Interrupt operations in the H8S/2138 Group and H8S/2134 Group differ depending on the interrupt control mode. NMI and address break interrupts are accepted at all times except in the reset ...

Page 178

Section 5 Interrupt Controller Figure 5.7 shows a block diagram of the priority decision circuit. acceptance control Interrupt source Interrupt control modes Figure 5.7 Block Diagram of Interrupt Control Operation Interrupt Acceptance Control and 3-Level Control: In interrupt control modes ...

Page 179

Table 5.6 Interrupts Selected in Each Interrupt Control Mode Interrupt Control Mode 0 1 Legend: *: Don’t care Default Priority Determination: The priority is determined for the selected interrupt, and a vector number is generated. If the same value is ...

Page 180

Section 5 Interrupt Controller 5.5.2 Interrupt Control Mode 0 Enabling and disabling of IRQ interrupts and on-chip supporting module interrupts can be set by means of the I bit in the CPU’s CCR, and ICR. Interrupts are enabled when the ...

Page 181

Program execution state Interrupt generated? Yes Control level 1 interrupt? Yes No IRQ0? No Yes IRQ1? Yes IICI1? Yes Save PC and CCR Read vector address Branch to interrupt handling routine Figure 5.8 Flowchart of Procedure Up to Interrupt Acceptance ...

Page 182

Section 5 Interrupt Controller 5.5.3 Interrupt Control Mode 1 Three-level masking is implemented for IRQ interrupts and on-chip supporting module interrupts by means of the I and UI bits in the CPU’s CCR, and ICR. Control level 0 interrupt requests ...

Page 183

Figure 5.10 shows a flowchart of the interrupt acceptance operation in this case interrupt source occurs when the corresponding interrupt enable bit is set interrupt request is sent to the interrupt controller. 2. When ...

Page 184

Section 5 Interrupt Controller Control level 1 interrupt? No IRQ0? Yes IRQ1 Figure 5.10 Flowchart of Procedure Up to Interrupt Acceptance in Rev. 4.00 Jun 06, 2006 page 128 of 1004 REJ09B0301-0400 Program execution state Interrupt generated? ...

Page 185

Interrupt Exception Handling Sequence Figure 5.11 shows the interrupt exception handling sequence. The example shown is for the case where interrupt control mode 0 is set in advanced mode, and the program area and stack area are in on-chip ...

Page 186

Section 5 Interrupt Controller Figure 5.11 Interrupt Exception Handling Rev. 4.00 Jun 06, 2006 page 130 of 1004 REJ09B0301-0400 ...

Page 187

Interrupt Response Times The H8S/2138 Group and H8S/2134 Group are capable of fast word access to on-chip memory, and high-speed processing can be achieved by providing the program area in on-chip ROM and the stack area in on-chip RAM. ...

Page 188

Section 5 Interrupt Controller 5.6 Usage Notes 5.6.1 Contention between Interrupt Generation and Disabling When an interrupt enable bit is cleared disable interrupts, the disabling becomes effective after execution of the instruction. In other words, when an ...

Page 189

The above contention will not occur if an enable bit or interrupt source flag is cleared to 0 while the interrupt is masked. 5.6.2 Instructions that Disable Interrupts Instructions that disable interrupts are LDC, ANDC, ORC, and XORC. After any ...

Page 190

Section 5 Interrupt Controller 5.7 DTC Activation by Interrupt 5.7.1 Overview The DTC can be activated by an interrupt. In this case, the following options are available: Interrupt request to CPU Activation request to DTC Both of the above For ...

Page 191

Operation The interrupt controller has three main functions in DTC control. Selection of Interrupt Source possible to select DTC activation request or CPU interrupt request with the DTCE bit of DTCERA to DTCERE in the DTC. After ...

Page 192

Section 5 Interrupt Controller Usage Note: SCI, IIC, and A/D converter interrupt sources are cleared when the DTC reads or writes to the prescribed register, and are not dependent upon the DISEL bit. Rev. 4.00 Jun 06, 2006 page 136 ...

Page 193

Section 6 Bus Controller 6.1 Overview The H8S/2138 Group and H8S/2134 Group have an on-chip bus controller (BSC) that allows external address space bus specifications, such as bus width and number of access states set. The bus controller ...

Page 194

Section 6 Bus Controller 6.1.2 Block Diagram Figure 6.1 shows a block diagram of the bus controller. External bus control signals WAIT Figure 6.1 Block Diagram of Bus Controller Rev. 4.00 Jun 06, 2006 page 138 of 1004 REJ09B0301-0400 Bus ...

Page 195

Pin Configuration Table 6.1 summarizes the pins of the bus controller. Table 6.1 Bus Controller Pins Name Symbol AS Address strobe IOS I/O select RD Read WR Write WAIT Wait 6.1.4 Register Configuration Table 6.2 summarizes the registers of ...

Page 196

Section 6 Bus Controller 6.2 Register Descriptions 6.2.1 Bus Control Register (BCR) 7 Bit ICIS1 ICIS0 Initial value 1 Read/Write R/W R/W BCR is an 8-bit readable/writable register that specifies the external memory space access mode, and the extent of ...

Page 197

Bit 4—Burst Cycle Select 1 (BRSTS1): Selects the number of burst cycles for the burst ROM interface. Bit 4 BRSTS1 Description 0 Burst cycle comprises 1 state 1 Burst cycle comprises 2 states Bit 3—Burst Cycle Select 0 (BRSTS0): Selects ...

Page 198

Section 6 Bus Controller Bit 7—RAM Select (RAMS)/Bit 6—RAM Area Setting (RAM0): These are reserved bits. Always write 0 when writing to these bits in the A-mask version. Bit 5—Bus Width Control (ABW): Specifies whether the external memory space is ...

Page 199

Bits 1 and 0—Wait Count 1 and 0 (WC1, WC0): These bits select the number of program wait states when external memory space is accessed while the AST bit is set to 1. Bit 1 Bit 0 WC1 WC0 Description ...

Page 200

Section 6 Bus Controller Table 6.3 Bus Specifications for Each Area (Basic Bus Interface) ABW AST WMS1 WMS0 WC1 0 0 — — — — —* —* Note: * Except when WMS1 = 0 and ...