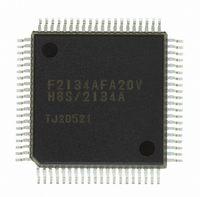

DF2134AFA20V Renesas Electronics America, DF2134AFA20V Datasheet - Page 588

DF2134AFA20V

Manufacturer Part Number

DF2134AFA20V

Description

IC H8S/2100 MCU FLASH 80QFP

Manufacturer

Renesas Electronics America

Series

H8® H8S/2100r

Datasheets

1.HEWH8E10A.pdf

(19 pages)

2.D12312SVTE25V.pdf

(341 pages)

3.DF2134AFA20V.pdf

(1063 pages)

Specifications of DF2134AFA20V

Core Processor

H8S/2000

Core Size

16-Bit

Speed

20MHz

Connectivity

IrDA, SCI

Peripherals

POR, PWM, WDT

Number Of I /o

58

Program Memory Size

128KB (128K x 8)

Program Memory Type

FLASH

Ram Size

4K x 8

Voltage - Supply (vcc/vdd)

4 V ~ 5.5 V

Data Converters

A/D 8x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-20°C ~ 75°C

Package / Case

80-QFP

For Use With

3DK2166 - DEV EVAL KIT H8S/2166

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2134AFA20V

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 588 of 1063

- Download datasheet (6Mb)

Section 17 Host Interface [H8S/2138 Group]

Bit 0—Output Buffer Full (OBF): Set to 1 when the slave processor writes to ODR1. Cleared to

0 when the host processor reads ODR1.

Bit 0

OBF

0

1

Table 17.3 shows the conditions for setting and clearing the STR1 flags.

Table 17.3 Set/Clear Timing for STR1 Flags

Flag

C/D

IBF *

OBF

Note:

17.2.7

IDR2 is an 8-bit read-only register to the slave processor, and an 8-bit write-only register to the

host processor. When CS2 is low, information on the host data bus is written into IDR2 at the

rising edge of IOW. The HA0 state is also latched into the C/D bit in STR2 to indicate whether the

written information is a command or data.

The initial values of IDR2 after a reset and in standby mode are undetermined.

Rev. 4.00 Jun 06, 2006 page 532 of 1004

REJ09B0301-0400

Bit

Initial value

Slave Read/Write

Host Read/Write

* The IBF flag setting and clearing conditions are different when the fast A20 gate is

Input Data Register 2 (IDR2)

used. For details see table 17.8, Fast A20 Gate Output Signals.

Description

[Clearing condition]

When the host processor reads ODR1 or the slave writes 0 in the OBF bit

[Setting condition]

When the slave processor writes to ODR1

Setting Condition

Rising edge of host’s write signal

(IOW) when HA0 is high

Rising edge of host’s write signal

(IOW) when writing to IDR1

Falling edge of slave’s internal write

signal (WR) when writing to ODR1

IDR7

—

W

R

7

IDR6

—

W

R

6

IDR5

—

W

R

5

IDR4

—

W

R

4

Clearing Condition

Rising edge of host’s write signal (IOW) when

HA0 is low

Falling edge of slave’s internal read signal

(RD) when reading IDR1

Rising edge of host’s read signal (IOR) when

reading ODR1

IDR3

—

W

R

3

IDR2

—

W

R

2

IDR1

—

W

R

1

(Initial value)

IDR0

—

W

R

0

Related parts for DF2134AFA20V

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: