DF2134AFA20V Renesas Electronics America, DF2134AFA20V Datasheet - Page 1017

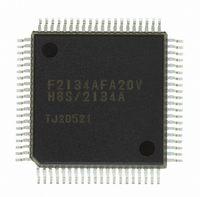

DF2134AFA20V

Manufacturer Part Number

DF2134AFA20V

Description

IC H8S/2100 MCU FLASH 80QFP

Manufacturer

Renesas Electronics America

Series

H8® H8S/2100r

Datasheets

1.HEWH8E10A.pdf

(19 pages)

2.D12312SVTE25V.pdf

(341 pages)

3.DF2134AFA20V.pdf

(1063 pages)

Specifications of DF2134AFA20V

Core Processor

H8S/2000

Core Size

16-Bit

Speed

20MHz

Connectivity

IrDA, SCI

Peripherals

POR, PWM, WDT

Number Of I /o

58

Program Memory Size

128KB (128K x 8)

Program Memory Type

FLASH

Ram Size

4K x 8

Voltage - Supply (vcc/vdd)

4 V ~ 5.5 V

Data Converters

A/D 8x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-20°C ~ 75°C

Package / Case

80-QFP

For Use With

3DK2166 - DEV EVAL KIT H8S/2166

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DF2134AFA20V

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 1017 of 1063

- Download datasheet (6Mb)

TCONRI—Timer Connection Register I

Bit

Initial value

Read/Write

SIMOD1

Input synchronization mode select 1 and 0

SIMOD1

R/W

7

0

0

1

SIMOD0

SIMOD0

Synchronization signal connection enable

R/W

SCONE

6

0

0

1

0

1

0

1

Input capture start bit

0

1

SCONE

No signal

S-on-G mode

Composite mode

Separate mode

Normal

connection

Synchronization

signal connec-

tion mode

Input synchronization signal inversion

The TICRR and TICRF input capture functions are stopped

[Clearing condition]

When a rising edge followed by a falling edge is detected on TMRIX

The TICRR and TICRF input capture functions are operating

(Waiting for detection of a rising edge followed by a falling edge on TMRIX)

[Setting condition]

When 1 is written in ICST after reading ICST = 0

R/W

0

1

5

0

Input synchronization signal inversion

Mode

0

1

The HFBACKI pin state is used directly as the HFBACKI input

The HFBACKI pin state is inverted before use as the HFBACKI input

Mode

The VFBACKI pin state is used directly as the VFBACKI input

The VFBACKI pin state is inverted before use as the VFBACKI input

ICST

R/W

4

0

FTIA

input

IVI

signal

FTIA

Input synchronization signal inversion

HFBACKI input

CSYNCI input

HSYNCI input

HSYNCI input

0

1

HFINV

Rev. 4.00 Jun 06, 2006 page 961 of 1004

R/W

H'FFFC

The HSYNCI and CSYNCI pin states are used

directly as the HSYNCI and CSYNCI inputs

The HSYNCI and CSYNCI pin states are inverted

before use as the HSYNCI and CSYNCI inputs

3

0

FTIB

FTIB

input

TMO1

signal

IHI signal

Appendix B Internal I/O Registers

VFINV

FTIC

input

VFBACKI

input

R/W

FTIC

2

0

VFBACKI input

PDC input

PDC input

VSYNCI input

Input synchronization

signal inversion

0

1

FTID

input

IHI

signal

HIINV

FTID

R/W

IVI signal

1

0

The VSYNCI pin state

is used directly as

the VSYNCI input

The VSYNCI pin state

is inverted before use

as the VSYNCI input

Timer Connection

REJ09B0301-0400

TMCI1

TMCI1

input

IHI

signal

VIINV

R/W

0

0

TMRI1

TMRI1

input

IVI

inverse

signal

Related parts for DF2134AFA20V

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: