EZ80F920120MOD Zilog, EZ80F920120MOD Datasheet - Page 250

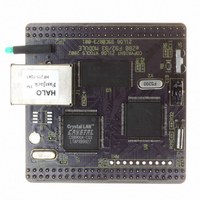

EZ80F920120MOD

Manufacturer Part Number

EZ80F920120MOD

Description

MODULE EZ80F92 512K 20MHZ

Manufacturer

Zilog

Datasheets

1.EZ80F920120MOD.pdf

(269 pages)

2.EZ80F920120MOD.pdf

(4 pages)

3.EZ80F920120MOD.pdf

(2 pages)

Specifications of EZ80F920120MOD

Module/board Type

Development Module

Processor Series

EZ80F92x

Core

eZ80

Data Bus Width

8 bit

Program Memory Type

Flash

Program Memory Size

1 MB

Interface Type

Cable

Maximum Clock Frequency

20 MHz

Operating Supply Voltage

0 V to 3.3 V

Maximum Operating Temperature

+ 70 C

Mounting Style

SMD/SMT

Package / Case

LQFP

Development Tools By Supplier

eZ80F920200ZCOG

Minimum Operating Temperature

0 C

For Use With/related Products

eZ80F92

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Other names

269-3157

EZ80F920120MOD

EZ80F920120MOD

- Current page: 250 of 269

- Download datasheet (4Mb)

PS015308-0404

External I/O Write Timing

Figure 60 and External I/O Write Timing diagram the timing for external I/O writes. Clock

rise/fall to signal transition timing is independent of the particular bus mode employed

(eZ80, Z80, Intel, or Motorola).

Figure 60.External I/O Write Timing

Table 152. External I/O Write Timing

Parameter

T

T

T

T

T

T

T

T

Note: *At the conclusion of a Write cycle, deassertion of WR always occurs before any change to

ADDR[23:0]

1

2

3

4

5

6

7

8

DATA[7:0]

(output)

IORQ

ADDR, DATA, CSx, or IORQ.

CSx

X

WR

IN

Abbreviation

Clock Rise to ADDR Valid Delay

Clock Rise to ADDR Hold Time

Clock Fall to Output DATA Valid Delay

Clock Rise to DATA Hold Time

Clock Rise to CSx Assertion Delay

Clock Rise to CSx Deassertion Delay

Clock Rise to IORQ Assertion Delay

Clock Rise to IORQ Deassertion Delay

T

7

T

1

T

5

P R E L I M I N A R Y

T

CLK

T

3

T

9

T

10

T

T

4

T

2

T

6

8

Product Specification

Min

Electrical Characteristics

2.0

2.0

2.0

2.0

2.0

2.0

—

—

eZ80F92/eZ80F93

Delay (ns)

Max

19.0

18.0

16.0

16.0

13

11

—

—

238

Related parts for EZ80F920120MOD

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Communication Controllers, ZILOG INTELLIGENT PERIPHERAL CONTROLLER (ZIP)

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

KIT DEV FOR Z8 ENCORE 16K TO 64K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

KIT DEV Z8 ENCORE XP 28-PIN

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

DEV KIT FOR Z8 ENCORE 8K/4K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

KIT DEV Z8 ENCORE XP 28-PIN

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

DEV KIT FOR Z8 ENCORE 4K TO 8K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

CMOS Z8 microcontroller. ROM 16 Kbytes, RAM 256 bytes, speed 16 MHz, 32 lines I/O, 3.0V to 5.5V

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Low-cost microcontroller. 512 bytes ROM, 61 bytes RAM, 8 MHz

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Z8 4K OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

CMOS SUPER8 ROMLESS MCU

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

SL1866 CMOSZ8 OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

SL1866 CMOSZ8 OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

OTP (KB) = 1, RAM = 125, Speed = 12, I/O = 14, 8-bit Timers = 2, Comm Interfaces Other Features = Por, LV Protect, Voltage = 4.5-5.5V

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Zilog, Inc.

Datasheet: