EZ80F920120MOD Zilog, EZ80F920120MOD Datasheet - Page 127

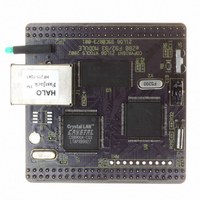

EZ80F920120MOD

Manufacturer Part Number

EZ80F920120MOD

Description

MODULE EZ80F92 512K 20MHZ

Manufacturer

Zilog

Datasheets

1.EZ80F920120MOD.pdf

(269 pages)

2.EZ80F920120MOD.pdf

(4 pages)

3.EZ80F920120MOD.pdf

(2 pages)

Specifications of EZ80F920120MOD

Module/board Type

Development Module

Processor Series

EZ80F92x

Core

eZ80

Data Bus Width

8 bit

Program Memory Type

Flash

Program Memory Size

1 MB

Interface Type

Cable

Maximum Clock Frequency

20 MHz

Operating Supply Voltage

0 V to 3.3 V

Maximum Operating Temperature

+ 70 C

Mounting Style

SMD/SMT

Package / Case

LQFP

Development Tools By Supplier

eZ80F920200ZCOG

Minimum Operating Temperature

0 C

For Use With/related Products

eZ80F92

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Other names

269-3157

EZ80F920120MOD

EZ80F920120MOD

- Current page: 127 of 269

- Download datasheet (4Mb)

PS015308-0404

UART Interrupt Enable Register

The UARTx_IER register is used to enable and disable the UART interrupts. The

UARTx_IER registers share the same I/O addresses as the UARTx_BRG_H registers. See

UART Interrupt Enable Registers (UART0_IER = 00C1h, UART1_IER = 00D1h).

Table 57. UART Interrupt Enable Registers

(UART0_IER = 00C1h, UART1_IER = 00D1h)

Bit

Reset

CPU Access

Note: R = Read Only; R/W = Read/Write.

Bit

Position

[7:5]

4

TCIE

3

MIIE

2

LSIE

1

TIE

0

RIE

Value

000

0

1

0

1

0

1

0

1

0

1

Description

Reserved.

Transmission complete interrupt is disabled.

Transmission complete interrupt is generated when both the

transmit hold register and the transmit shift register are empty.

Modem interrupt on edge detect of status inputs is disabled.

Modem interrupt on edge detect of status inputs is enabled.

Line status interrupt is disabled.

Line status interrupt is enabled for receive data errors:

incorrect parity bit received, framing error, overrun error, or

break detection.

Transmit interrupt is disabled.

Transmit interrupt is enabled. Interrupt is generated when the

transmit FIFO/buffer is empty indicating no more bytes

available for transmission.

Receive interrupt is disabled.

Receive interrupt and receiver time-out interrupt are enabled.

Interrupt is generated if the FIFO/buffer contains data ready to

be read or if the receiver times out.

P R E L I M I N A R Y

R

7

0

R

6

0

R

5

0

Universal Asynchronous Receiver/Transmitter

R/W

4

0

R/W

3

0

Product Specification

R/W

2

0

eZ80F92/eZ80F93

R/W

1

0

R/W

0

0

115

Related parts for EZ80F920120MOD

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Communication Controllers, ZILOG INTELLIGENT PERIPHERAL CONTROLLER (ZIP)

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

KIT DEV FOR Z8 ENCORE 16K TO 64K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

KIT DEV Z8 ENCORE XP 28-PIN

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

DEV KIT FOR Z8 ENCORE 8K/4K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

KIT DEV Z8 ENCORE XP 28-PIN

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

DEV KIT FOR Z8 ENCORE 4K TO 8K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

CMOS Z8 microcontroller. ROM 16 Kbytes, RAM 256 bytes, speed 16 MHz, 32 lines I/O, 3.0V to 5.5V

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Low-cost microcontroller. 512 bytes ROM, 61 bytes RAM, 8 MHz

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Z8 4K OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

CMOS SUPER8 ROMLESS MCU

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

SL1866 CMOSZ8 OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

SL1866 CMOSZ8 OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

OTP (KB) = 1, RAM = 125, Speed = 12, I/O = 14, 8-bit Timers = 2, Comm Interfaces Other Features = Por, LV Protect, Voltage = 4.5-5.5V

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Zilog, Inc.

Datasheet: