EZ80F920120MOD Zilog, EZ80F920120MOD Datasheet - Page 212

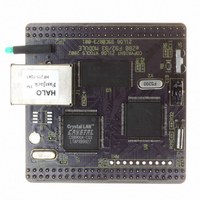

EZ80F920120MOD

Manufacturer Part Number

EZ80F920120MOD

Description

MODULE EZ80F92 512K 20MHZ

Manufacturer

Zilog

Datasheets

1.EZ80F920120MOD.pdf

(269 pages)

2.EZ80F920120MOD.pdf

(4 pages)

3.EZ80F920120MOD.pdf

(2 pages)

Specifications of EZ80F920120MOD

Module/board Type

Development Module

Processor Series

EZ80F92x

Core

eZ80

Data Bus Width

8 bit

Program Memory Type

Flash

Program Memory Size

1 MB

Interface Type

Cable

Maximum Clock Frequency

20 MHz

Operating Supply Voltage

0 V to 3.3 V

Maximum Operating Temperature

+ 70 C

Mounting Style

SMD/SMT

Package / Case

LQFP

Development Tools By Supplier

eZ80F920200ZCOG

Minimum Operating Temperature

0 C

For Use With/related Products

eZ80F92

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Other names

269-3157

EZ80F920120MOD

EZ80F920120MOD

- Current page: 212 of 269

- Download datasheet (4Mb)

PS015308-0404

Erasing Flash Memory

Flash Control Registers

the 16ms maximum cumulative programming time between erasures is not exceeded for a

row.

Memory Write

A single-byte memory Write operation uses the address bus and data bus of the eZ80F92

device for programming a single data byte to Flash. While the CPU executes a LOAD

instruction, the Flash controller asserts the internal WAIT signal to stall the CPU until the

Write is complete. A single-byte Write takes between 66µs and 85µs to complete. Pro -

gramming an entire row using memory Writes therefore takes at most 10.8ms. This time

does not include time required by the CPU to transfer data to the registers which is a func-

tion of the instructions employed and the system clock frequency.

The memory Write function does not support multibyte row programming. Because mem-

ory Writes are self-timed, they can be performed back-to-back without any necessity for

polling or interrupts.

Erasing bytes in Flash memory returns them to a value of FFh. Both the Mass and Page

Erase operations are self-timed by the Flash controller, leaving the CPU free to execute

other operations in parallel. The DONE status bit in the Flash Interrupt Control Register

can be polled by software or used as an interrupt source to signal completion of an Erase

operation. If the CPU attempts to access Flash while an Erase is in progress, the Flash con-

troller forces a WAIT state until the Erase operation completes.

Mass Erase

Performing a Mass Erase operation on Flash memory erases all bits in Flash, including the

Information Page. This self-timed operation takes approximately 200 ms to complete.

Page Erase

The smallest erasable unit in Flash memory is a page. Which of the main Flash memory

pages or the single Information Page is to be erased is determined by the setting of the

FLASH_PAGE register. This self-timed operation takes approximately 10 ms to complete.

The Flash register interface contains all the registers used in Flash memory. The defini-

tions below describe each register.

Flash Key Register

Writing the two-byte sequence

the Flash Divider and Flash Write/Erase Protection registers. If these values are not writ-

P R E L I M I N A R Y

B6h

,

49h

in immediate succession to this register unlocks

Product Specification

eZ80F92/eZ80F93

Flash Memory

200

Related parts for EZ80F920120MOD

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Communication Controllers, ZILOG INTELLIGENT PERIPHERAL CONTROLLER (ZIP)

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

KIT DEV FOR Z8 ENCORE 16K TO 64K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

KIT DEV Z8 ENCORE XP 28-PIN

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

DEV KIT FOR Z8 ENCORE 8K/4K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

KIT DEV Z8 ENCORE XP 28-PIN

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

DEV KIT FOR Z8 ENCORE 4K TO 8K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

CMOS Z8 microcontroller. ROM 16 Kbytes, RAM 256 bytes, speed 16 MHz, 32 lines I/O, 3.0V to 5.5V

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Low-cost microcontroller. 512 bytes ROM, 61 bytes RAM, 8 MHz

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Z8 4K OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

CMOS SUPER8 ROMLESS MCU

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

SL1866 CMOSZ8 OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

SL1866 CMOSZ8 OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

OTP (KB) = 1, RAM = 125, Speed = 12, I/O = 14, 8-bit Timers = 2, Comm Interfaces Other Features = Por, LV Protect, Voltage = 4.5-5.5V

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Zilog, Inc.

Datasheet: