EZ80F920120MOD Zilog, EZ80F920120MOD Datasheet - Page 198

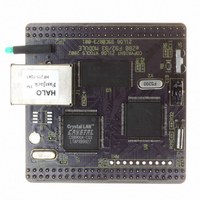

EZ80F920120MOD

Manufacturer Part Number

EZ80F920120MOD

Description

MODULE EZ80F92 512K 20MHZ

Manufacturer

Zilog

Datasheets

1.EZ80F920120MOD.pdf

(269 pages)

2.EZ80F920120MOD.pdf

(4 pages)

3.EZ80F920120MOD.pdf

(2 pages)

Specifications of EZ80F920120MOD

Module/board Type

Development Module

Processor Series

EZ80F92x

Core

eZ80

Data Bus Width

8 bit

Program Memory Type

Flash

Program Memory Size

1 MB

Interface Type

Cable

Maximum Clock Frequency

20 MHz

Operating Supply Voltage

0 V to 3.3 V

Maximum Operating Temperature

+ 70 C

Mounting Style

SMD/SMT

Package / Case

LQFP

Development Tools By Supplier

eZ80F920200ZCOG

Minimum Operating Temperature

0 C

For Use With/related Products

eZ80F92

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Other names

269-3157

EZ80F920120MOD

EZ80F920120MOD

- Current page: 198 of 269

- Download datasheet (4Mb)

PS015308-0404

ZDI Read Register Low, High, and Upper

The ZDI register Read Only address space offers Low, High, and Upper functions, which

contain the value read by a Read operation from the ZDI Read/Write Control register

(ZDI_RW_CTL). This data is valid only while in ZDI BREAK mode and only if the

instruction is read by a request from the ZDI Read/Write Control register. See ZDI Read

Register Low, High and Upper (ZDI_RD_L = 10h, ZDI_RD_H = 11h, and ZDI_RD_U =

12h in the ZDI Register Read Only Address Space).

Table 108. ZDI Read Register Low, High and Upper

(ZDI_RD_L = 10h, ZDI_RD_H = 11h, and ZDI_RD_U = 12h in the ZDI Register Read

Only Address Space)

Bit

Position

4

ADL

3

MADL

2

IEF1

[1:0]

Bit

Reset

CPU Access

Note: R = Read Only.

Bit

Position

[7:0]

ZDI_RD_L,

ZDI_RD_H, or

ZDI_RD_U

Value Description

0

1

0

1

0

1

00

Value Description

00h–

FFh

P R E L I M I N A R Y

R

7

0

The CPU is operating in Z80 MEMORY mode.

(ADL bit = 0)

The CPU is operating in ADL MEMORY mode.

(ADL bit = 1)

The CPU’s Mixed-Memory mode (MADL) bit is reset to 0.

The CPU’s Mixed-Memory mode (MADL) bit is set to 1.

The CPU’s Interrupt Enable Flag 1 is reset to 0. Maskable

interrupts are disabled.

The CPU’s Interrupt Enable Flag 1 is set to 1. Maskable

interrupts are enabled.

Reserved.

Values read from the memory location as requested by

the ZDI Read Control register during a ZDI Read

operation. The 24-bit value is supplied by {ZDI_RD_U,

ZDI_RD_H, ZDI_RD_L}.

R

6

0

R

5

0

R

4

0

R

3

0

Product Specification

R

ZiLOG Debug Interface

2

0

eZ80F92/eZ80F93

R

1

0

R

0

0

186

Related parts for EZ80F920120MOD

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Communication Controllers, ZILOG INTELLIGENT PERIPHERAL CONTROLLER (ZIP)

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

KIT DEV FOR Z8 ENCORE 16K TO 64K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

KIT DEV Z8 ENCORE XP 28-PIN

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

DEV KIT FOR Z8 ENCORE 8K/4K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

KIT DEV Z8 ENCORE XP 28-PIN

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

DEV KIT FOR Z8 ENCORE 4K TO 8K

Manufacturer:

Zilog

Datasheet:

Part Number:

Description:

CMOS Z8 microcontroller. ROM 16 Kbytes, RAM 256 bytes, speed 16 MHz, 32 lines I/O, 3.0V to 5.5V

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Low-cost microcontroller. 512 bytes ROM, 61 bytes RAM, 8 MHz

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Z8 4K OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

CMOS SUPER8 ROMLESS MCU

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

SL1866 CMOSZ8 OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

SL1866 CMOSZ8 OTP Microcontroller

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

OTP (KB) = 1, RAM = 125, Speed = 12, I/O = 14, 8-bit Timers = 2, Comm Interfaces Other Features = Por, LV Protect, Voltage = 4.5-5.5V

Manufacturer:

Zilog, Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Zilog, Inc.

Datasheet: