HD6413007F20 Renesas Electronics America, HD6413007F20 Datasheet - Page 134

HD6413007F20

Manufacturer Part Number

HD6413007F20

Description

IC H8 MCU ROMLESS 5V 100QFP

Manufacturer

Renesas Electronics America

Series

H8® H8/300Hr

Datasheet

1.D13007F20V.pdf

(798 pages)

Specifications of HD6413007F20

Core Processor

H8/300H

Core Size

16-Bit

Speed

20MHz

Connectivity

SCI, SmartCard

Peripherals

DMA, PWM, WDT

Number Of I /o

35

Program Memory Type

ROMless

Ram Size

4K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 8x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-20°C ~ 75°C

Package / Case

100-QFP

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Eeprom Size

-

Program Memory Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 134 of 798

- Download datasheet (5Mb)

5. Interrupt Controller

5.5

5.5.1

When an instruction clears an interrupt enable bit to 0 to disable the interrupt, the interrupt is not

disabled until after execution of the instruction is completed. If an interrupt occurs while a BCLR,

MOV, or other instruction is being executed to clear its interrupt enable bit to 0, at the instant

when execution of the instruction ends the interrupt is still enabled, so its interrupt exception

handling is carried out. If a higher-priority interrupt is also requested, however, interrupt exception

handling for the higher-priority interrupt is carried out, and the lower-priority interrupt is ignored.

This also applies to the clearing of an interrupt flag to 0.

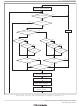

Figure 5.8 shows an example in which an IMIEA bit is cleared to 0 in the 16-bit timer's TISRA

register.

This type of contention will not occur if the interrupt is masked when the interrupt enable bit or

flag is cleared to 0.

Rev.5.00 Sep. 12, 2007 Page 104 of 764

REJ09B0396-0500

φ

Internal

address bus

Internal

write signal

IMIEA

IMIA

IMFA interrupt

signal

Figure 5.8 Contention between Interrupt and Interrupt-Disabling Instruction

Usage Notes

Contention between Interrupt and Interrupt-Disabling Instruction

TISRA write cycle by CPU

TISRA address

IMIA exception handling

Related parts for HD6413007F20

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: