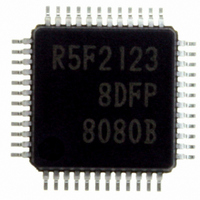

R5F21238DFP#U0 Renesas Electronics America, R5F21238DFP#U0 Datasheet - Page 414

R5F21238DFP#U0

Manufacturer Part Number

R5F21238DFP#U0

Description

IC R8C/23 MCU FLASH 48-LQFP

Manufacturer

Renesas Electronics America

Series

R8C/2x/23r

Specifications of R5F21238DFP#U0

Core Size

16/32-Bit

Program Memory Size

64KB (64K x 8)

Peripherals

POR, Voltage Detect, WDT

Core Processor

R8C

Speed

20MHz

Connectivity

CAN, I²C, LIN, SIO, SSU, UART/USART

Number Of I /o

41

Program Memory Type

FLASH

Ram Size

3K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 12x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

48-LQFP

No. Of I/o's

41

Ram Memory Size

3KB

Cpu Speed

20MHz

No. Of Timers

4

Digital Ic Case Style

LQFP

Embedded Interface Type

CAN, I2C, UART

Rohs Compliant

Yes

Cpu Family

R8C

Device Core Size

16b

Frequency (max)

20MHz

Interface Type

I2C/UART

Total Internal Ram Size

3KB

# I/os (max)

41

Number Of Timers - General Purpose

5

Operating Supply Voltage (typ)

3.3/5V

Operating Supply Voltage (max)

5.5V

Operating Supply Voltage (min)

3V

On-chip Adc

12-chx10-bit

Instruction Set Architecture

CISC

Operating Temp Range

-40C to 85C

Operating Temperature Classification

Industrial

Mounting

Surface Mount

Pin Count

48

Package Type

LQFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

RCDK8C - KIT DEV EVAL FOR CAN R8C/23R0K521237S000BE - KIT DEV RSK R8C/23R0E521237CPE00 - EMULATOR COMPACT R8C/20/21/22/23

Eeprom Size

-

Lead Free Status / Rohs Status

Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 414 of 551

- Download datasheet (6Mb)

R8C/22 Group, R8C/23 Group

Rev.2.00 Aug 20, 2008

REJ09B0251-0200

Figure 18.24

18.12.1 Reception

CANbus

RecReq bit

InvalData bit

NewData bit

MsgLost bit

CAN0 successful

reception

interrupt

RecState bit

RecSucc bit

MBOX bit

(1) If a SOF is detected on the CAN bus, the RecState bit in the C0STR register is set to 1 (During reception)

(2) The message successfully is received and the NewData bit in the C0MCTLi register of the reception slot is

(3) If the interrupt enable bit in the C0ICR register of the slot is set to 1 (interrupt enabled), the CAN0

(4) Set the NewData bit to 0 (the content of the slot is read out or still under processing by the CPU) by a

(5) When next CAN message is received before the NewData bit is set to 0 by a program or a receive request to

Figure 18.24 shows the Timing of Receive Data Frame Sequence. This is an operation example when

consecutive messages are received.

immediately and the slot starts receiving a message.

set to 1 (stored new data in slot). The InvalData bit in the C0MCTLi register is set to 1 (the message is

being updated) at the same time and set to 0 (the message is valid) after the message completely is stored to

the slot.

successful reception interrupt request is generated and the MBOX and RecSucc bits in the C0STR register

change.

program and read the message from the slot.

a slot is canceled, the MsgLost bit in the C0MCTLj register is set to 1 (this slot already contained a

message) and new message is stored in a slot. CAN0 successful reception interrupt and the C0STR register

change the same as (3).

i = 0 to 15

Timing of Receive Data Frame Sequence

SOF

(1)

Page 392 of 501

ACK

EOF

(2)

(2)

(3)

IFS

SOF

Receive slot No.

(4)

ACK

EOF

(5)

(5)

(5)

18. CAN Module

IFS

Related parts for R5F21238DFP#U0

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: