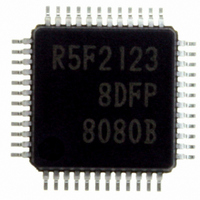

R5F21238DFP#U0 Renesas Electronics America, R5F21238DFP#U0 Datasheet - Page 315

R5F21238DFP#U0

Manufacturer Part Number

R5F21238DFP#U0

Description

IC R8C/23 MCU FLASH 48-LQFP

Manufacturer

Renesas Electronics America

Series

R8C/2x/23r

Specifications of R5F21238DFP#U0

Core Size

16/32-Bit

Program Memory Size

64KB (64K x 8)

Peripherals

POR, Voltage Detect, WDT

Core Processor

R8C

Speed

20MHz

Connectivity

CAN, I²C, LIN, SIO, SSU, UART/USART

Number Of I /o

41

Program Memory Type

FLASH

Ram Size

3K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 12x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

48-LQFP

No. Of I/o's

41

Ram Memory Size

3KB

Cpu Speed

20MHz

No. Of Timers

4

Digital Ic Case Style

LQFP

Embedded Interface Type

CAN, I2C, UART

Rohs Compliant

Yes

Cpu Family

R8C

Device Core Size

16b

Frequency (max)

20MHz

Interface Type

I2C/UART

Total Internal Ram Size

3KB

# I/os (max)

41

Number Of Timers - General Purpose

5

Operating Supply Voltage (typ)

3.3/5V

Operating Supply Voltage (max)

5.5V

Operating Supply Voltage (min)

3V

On-chip Adc

12-chx10-bit

Instruction Set Architecture

CISC

Operating Temp Range

-40C to 85C

Operating Temperature Classification

Industrial

Mounting

Surface Mount

Pin Count

48

Package Type

LQFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

RCDK8C - KIT DEV EVAL FOR CAN R8C/23R0K521237S000BE - KIT DEV RSK R8C/23R0E521237CPE00 - EMULATOR COMPACT R8C/20/21/22/23

Eeprom Size

-

Lead Free Status / Rohs Status

Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 315 of 551

- Download datasheet (6Mb)

R8C/22 Group, R8C/23 Group

Rev.2.00 Aug 20, 2008

REJ09B0251-0200

16.2

Table 16.2

NOTE:

Transfer Data Format

Operating Mode

Master / Slave Device

I/O Pin

Transfer Clock

Receive Error Detection • Overrun error

Multimaster Error

Detection

Interrupt Request

Select Function

The serial data of the clock synchronous can communicate for the clock synchronous serial I/O with chip select.

Table 16.2 lists the Clock Synchronous Serial I/O with Chip Select Specifications and Figure 16.1 shows a Block

Diagram of Clock Synchronous Serial I/O with Chip Select.

Figures 16.2 to 16.9 show Clock Synchronous Serial I/O with Chip Select Associated Registers.

1. The interrupt vector table is one of the clock synchronous serial I/O with chip select specification.

Clock Synchronous Serial I/O with Chip Select (SSU)

Item

Clock Synchronous Serial I/O with Chip Select Specifications

Page 293 of 501

• Transfer-data length 8 bits

• Clock synchronous communication mode

• 4-wire bus communication mode (including bidirectional communication)

Selectable

SSCK (I/O): Clock I/O pin

SSI (I/O): Data I/O pin

SSO (I/O): Data I/O pin

SCS (I/O): Chip-select I/O pin

• When the MSS bit in the SSCRH register is set to 0 (operates as slave

• When the MSS bit in the SSCRH register is set to 1 (operates as master

• Clock polarity and phase of SSCK can be selected.

• Conflict error

5 interrupt requests (transmit-end, transmit-data-empty, receive-data-full,

overrun error and conflict error).

• Data transfer direction

• SSCK clock polarity

• SSCK clock phase

device), external clock can be selected.

device), internal clock (selects from f1/256, f1/128, f1/64, f1/32, f1/16, f1/8 and

f1/4 and outputs from SSCK pin) can be selected.

Continuous transmit and receive of serial data are enabled since both

transmitter and receiver have buffer structure.

Overrun error occurs during receive and completes by error. While the RDRF

bit in the SSSR register is set to 1 (data in the SSRDR register) and

completing the next serial data receive, the ORER bit is set to 1.

While the SSUMS bit in the SSMR2 register is set to 1 (4-wire bus

communication mode) and the MSS bit in the SSCRH register is set to 1

(operates as master device) and when starting a serial communication, the

CE bit in the SSSR register is set to 1 if “L” applies to the SCS pin input.

When the SSUMS bit in the SSMR2 register is set to 1 (4-wire bus

communication mode), the MSS bit in the SSCRH register is set to 0

(operates as slave device) and the SCS pin input changes state from “L” to

“H”, the CE bit in the SSSR register is set to 1.

Selects MSB-first or LSB-first

Selects “L” or “H” level when clock stops

Selects edge of data change and data download

(1)

Specification

16. Clock Synchronous Serial Interface

Related parts for R5F21238DFP#U0

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: