R8A77850ANBGV Renesas Electronics America, R8A77850ANBGV Datasheet - Page 546

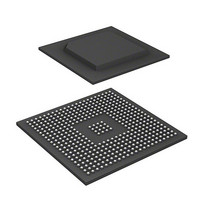

R8A77850ANBGV

Manufacturer Part Number

R8A77850ANBGV

Description

IC SUPERH MPU ROMLESS 436-BGA

Manufacturer

Renesas Electronics America

Series

SuperH® SH7780r

Datasheet

1.R8A77850AADBGV.pdf

(1694 pages)

Specifications of R8A77850ANBGV

Core Processor

SH-4A

Core Size

32-Bit

Speed

600MHz

Connectivity

Audio Codec, MMC, Serial Sound, SCI, SIO, SPI, SSI

Peripherals

DMA, POR, WDT

Number Of I /o

108

Program Memory Type

ROMless

Ram Size

8K x 8

Voltage - Supply (vcc/vdd)

1 V ~ 1.2 V

Oscillator Type

External

Operating Temperature

-20°C ~ 75°C

Package / Case

436-BGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Data Converters

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

R8A77850ANBGV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 546 of 1694

- Download datasheet (9Mb)

12. DDR2-SDRAM Interface (DBSC2)

16-bit external bus

32-bit external bus

(2)

In order to utilize DDR2-SDRAM multibank functions to reduce SDRAM command vacant cycles

insofar as possible and improve the efficiency of bus use, the DBSC2 issues in advance a

PRE/ACT command corresponding to the following request queue page miss processing. Only the

PRE/ACT command is issued in advance, so there is no change in the read/write order. A

PRE/ACT command is issued in advance only when the following request (1) results in a page

miss, and moreover (2) entails access of a bank different from that of the request currently being

processed. Figure 12.6 shows an example of execution of preceding precharge/activate processing.

This is an example of a command issued to the SDRAM when the external data bus width is 32

bits, the PRE/ACT minimum time constraint is 3 cycles, the ACT-READ/WRITE minimum time

constraint is 3 cycles, and the ACT (A)-ACT (B) minimum time constraint is 2 cycles. In this

example, the first through fourth requests are accumulated, and the first request is the request

initially provided to the queue.

First, at time 1 the DBSC2 issues to the SDRAM a PRE command for the first read (16-byte)

request processing. Then, when determining the command to be issued at time 2, due to timing

constraints it is not possible to issue at time 2 the ACT command necessary as request processing

for the first read (16-byte) request, which has higher priority. Hence the DBSC2 searches for a

Rev.1.00 Jan. 10, 2008 Page 514 of 1658

REJ09B0261-0100

Read (1, 2, 4, or 8 bytes)

Read (16 bytes)

Read (32 bytes)

Write (1, 2, 4, or 8 bytes)

Write (16 bytes)

Write (32 bytes)

Read (1, 2, 4, 8, or 16 bytes)

Read (32 bytes)

Write (1, 2, 4, 8, or 16 bytes)

Write (32 bytes)

Preceding Precharge/Activate Processing

Figure 12.5 Read/Write Command Issued to the SDRAM in Response

1 command

2 commands

4 commands

1 command

2 commands

4 commands

1 command

2 commands

1 command

2 commands

to the Request from the SuperHyway Bus

1st cycle

Read

Read

Read

Write

Write

Write

Read

Read

Write

Write

2nd cycle

DSEL

DSEL

DSEL

DSEL

DSEL

DSEL

3rd cycle

Read

Read

Write

Write

Read

Write

4th cycle

DSEL

DSEL

5th cycle

Read

Write

6th cycle

DSEL

DSEL

7th cycle

Read

Write

Related parts for R8A77850ANBGV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: