R8A77850ANBGV Renesas Electronics America, R8A77850ANBGV Datasheet - Page 1485

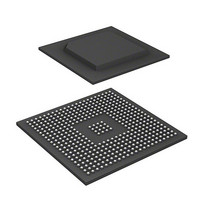

R8A77850ANBGV

Manufacturer Part Number

R8A77850ANBGV

Description

IC SUPERH MPU ROMLESS 436-BGA

Manufacturer

Renesas Electronics America

Series

SuperH® SH7780r

Datasheet

1.R8A77850AADBGV.pdf

(1694 pages)

Specifications of R8A77850ANBGV

Core Processor

SH-4A

Core Size

32-Bit

Speed

600MHz

Connectivity

Audio Codec, MMC, Serial Sound, SCI, SIO, SPI, SSI

Peripherals

DMA, POR, WDT

Number Of I /o

108

Program Memory Type

ROMless

Ram Size

8K x 8

Voltage - Supply (vcc/vdd)

1 V ~ 1.2 V

Oscillator Type

External

Operating Temperature

-20°C ~ 75°C

Package / Case

436-BGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Data Converters

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

R8A77850ANBGV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 1485 of 1694

- Download datasheet (9Mb)

The user break controller (UBC) provides versatile functions to facilitate program debugging.

These functions help to ease creation of a self-monitor/debugger, which allows easy program

debugging using this LSI alone, without using the in-circuit emulator. Various break conditions

can be set in the UBC: instruction fetch or read/write access of an operand, operand size, data

contents, address value, and program stop timing for instruction fetch.

29.1

1. The following break conditions can be set.

• Address

• Data

• Bus cycle

• Read or write access

• Operand sizes

2. The user-designated exception handling routine for the user break condition can be executed.

3. Pre-instruction-execution or post-instruction-execution can be selected as the PC break timing.

4. A maximum of 2

Break channels: Two (channels 0 and 1)

User break conditions can be set independently for channels 0 and 1, and can also be set as a

single sequential condition for the two channels, that is, a sequential break. (Sequential break

involves two cases such that the channel 0 break condition is satisfied in a certain bus cycle

and then the channel 1 break condition is satisfied in a different bus cycle, and vice versa.)

When 40 bits containing ASID and 32-bit address are compared with the specified value, all

the ASID bits can be compared or masked.

32-bit address can be masked bit by bit, allowing the user to mask the address in desired page

sizes such as lower 12 bits (4-Kbyte page) and lower 10 bits (1-Kbyte page).

32 bits can be masked only for channel 1.

The program can break either for instruction fetch (PC break) or operand access.

Byte, word, longword, and quadword are supported.

for channel 1).

Features

Section 29 User Break Controller (UBC)

12

– 1 repetition counts can be specified as the break condition (available only

Rev.1.00 Jan. 10, 2008 Page 1453 of 1658

29. User Break Controller (UBC)

REJ09B0261-0100

Related parts for R8A77850ANBGV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: