R8A77850ANBGV Renesas Electronics America, R8A77850ANBGV Datasheet - Page 1106

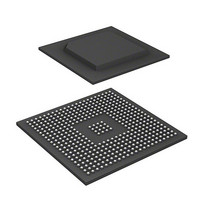

R8A77850ANBGV

Manufacturer Part Number

R8A77850ANBGV

Description

IC SUPERH MPU ROMLESS 436-BGA

Manufacturer

Renesas Electronics America

Series

SuperH® SH7780r

Datasheet

1.R8A77850AADBGV.pdf

(1694 pages)

Specifications of R8A77850ANBGV

Core Processor

SH-4A

Core Size

32-Bit

Speed

600MHz

Connectivity

Audio Codec, MMC, Serial Sound, SCI, SIO, SPI, SSI

Peripherals

DMA, POR, WDT

Number Of I /o

108

Program Memory Type

ROMless

Ram Size

8K x 8

Voltage - Supply (vcc/vdd)

1 V ~ 1.2 V

Oscillator Type

External

Operating Temperature

-20°C ~ 75°C

Package / Case

436-BGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Data Converters

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

R8A77850ANBGV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 1106 of 1694

- Download datasheet (9Mb)

21. Serial Communication Interface with FIFO (SCIF)

21.4.2

In asynchronous mode, a character that consists of data with a start bit indicating the start of

communication and a stop bit indicating the end of communication is transmitted or received. In

this mode, serial communication is performed with synchronization achieved character by

character.

Inside the SCIF, the transmitter and receiver are independent units, enabling full-duplex

communication. Both the transmitter and receiver have a 64-stage FIFO buffer structure, so that

data can be read or written during transmission or reception, enabling continuous data

transmission and reception.

Figure 21.7 shows the general format for asynchronous serial communication.

In asynchronous serial communication, the transmission line is usually held in the mark state (high

level). The SCIF monitors the transmission line, and when it goes to the space state (low level),

recognizes a start bit and starts serial communication.

One character in serial communication consists of a start bit (low level), followed by

transmit/receive data (LSB first; from the lowest bit), a parity bit (high or low level), and finally

stop bits (high level).

In reception in asynchronous mode, the SCIF synchronizes with the fall of the start bit. Receive

data can be latched at the middle of each bit because the SCIF samples data at the eighth clock

with frequency of 16 times the bit rate.

Rev.1.00 Jan. 10, 2008 Page 1074 of 1658

REJ09B0261-0100

(mark state)

Serial

data

Operation in Asynchronous Mode

Idle state

1

1 bit

Figure 21.7 Data Format in Asynchronous Communication

Start

bit

0

(Example with 8-Bit Data, Parity, and Two Stop Bits)

LSB

D0

D1

One unit of transfer data (character or frame)

D2

Transmit/receive data

D3

7 or 8 bits

D4

D5

D6

MSB

D7

1 bit or

none

Parity

0/1

bit

Stop bit

1

1 or 2 bits

1

(mark state)

Idle state

1

Related parts for R8A77850ANBGV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: