R8A77850ANBGV Renesas Electronics America, R8A77850ANBGV Datasheet - Page 1272

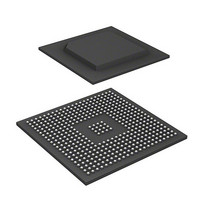

R8A77850ANBGV

Manufacturer Part Number

R8A77850ANBGV

Description

IC SUPERH MPU ROMLESS 436-BGA

Manufacturer

Renesas Electronics America

Series

SuperH® SH7780r

Datasheet

1.R8A77850AADBGV.pdf

(1694 pages)

Specifications of R8A77850ANBGV

Core Processor

SH-4A

Core Size

32-Bit

Speed

600MHz

Connectivity

Audio Codec, MMC, Serial Sound, SCI, SIO, SPI, SSI

Peripherals

DMA, POR, WDT

Number Of I /o

108

Program Memory Type

ROMless

Ram Size

8K x 8

Voltage - Supply (vcc/vdd)

1 V ~ 1.2 V

Oscillator Type

External

Operating Temperature

-20°C ~ 75°C

Package / Case

436-BGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Data Converters

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

R8A77850ANBGV

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 1272 of 1694

- Download datasheet (9Mb)

24. Multimedia Card Interface (MMCIF)

24.6

24.6.1

In order to transfer data in FIFO with the DMAC, set MMCIF (DMACR) after setting the

DMAC*. Transmit the read command after setting DMACR.

Figure 24.22 to 24.24 shows the operational flow for a read sequence.

• Clear FIFO and make settings in DMACR.

• Read command transmission is started.

• Command response is received from the card.

• Read data is received from the card.

• After the read sequence, data remains in FIFO. If necessary, write 100 to SET[2:0] in DMACR

• Confirm that the DMAC transfer is completed and set the DMAEN bit in DMACR to 0.

• Set the CMDOFF bit to 1 and clear DMACR to H'00 if a CRC error (CRCERI) or a command

• Set the CMDOFF bit to 1, clear DMACR to H'00, and clear FIFO if a CRC error (CRCERI) or

When using DMA, next block read is resumed automatically when the AUTO bit in DMACR is

set to 1 and normal read is detected after the block transfer end of a pre-defined multiple block

transfer. Figure 24.25 shows the operational flow for a pre-defined multiple block read using auto-

mode.

• Clear FIFO.

• Set the block number to (TBNCR).

• Set DMACR.

• Read command transmission is started.

• Command response is received from the card.

• Read data is received from the card.

• Detect the command timeout error (CTERI) if a command response is not received from the

• The end of the command sequence is detected by poling the BUSY flag in CSTR or through

Rev.1.00 Jan. 10, 2008 Page 1240 of 1658

REJ09B0261-0100

to read all data from FIFO.

timeout error (CTERI) occurs in the command response reception.

a data timeout error (DTERI) occurs in the read data reception.

card.

the pre-defined multiple block transfer end flag (BTI).

Operations when Using DMA

Operation in Read Sequence

Related parts for R8A77850ANBGV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: