ATSAM3U4CA-CU Atmel, ATSAM3U4CA-CU Datasheet - Page 628

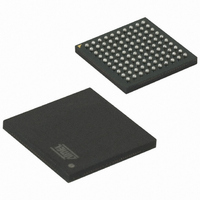

ATSAM3U4CA-CU

Manufacturer Part Number

ATSAM3U4CA-CU

Description

IC MCU 32BIT 256KB FLSH 100TFBGA

Manufacturer

Atmel

Series

SAM3Ur

Specifications of ATSAM3U4CA-CU

Core Processor

ARM® Cortex-M3™

Core Size

32-Bit

Speed

96MHz

Connectivity

EBI/EMI, I²C, MMC, SPI, SSC, UART/USART, USB

Peripherals

Brown-out Detect/Reset, DMA, I²S, POR, PWM, WDT

Number Of I /o

57

Program Memory Size

256KB (256K x 8)

Program Memory Type

FLASH

Ram Size

52K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 1.95 V

Data Converters

A/D 4x10b, 4x12b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-TFBGA

Processor Series

ATSAM3x

Core

ARM Cortex M3

Data Bus Width

32 bit

Data Ram Size

52 KB

Interface Type

3xUSART, TWI, 4xSPI, Bus

Maximum Clock Frequency

96 MHz

Number Of Programmable I/os

57

Number Of Timers

8

Operating Supply Voltage

1.62 V to 3.6 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

JTRACE-CM3, MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

ATSAM3U-EK

Minimum Operating Temperature

- 40 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

ATSAM3U4CA-CU

Manufacturer:

ATMEL/爱特梅尔

Quantity:

20 000

- Current page: 628 of 1171

- Download datasheet (25Mb)

Figure 33-10. Master Read with Multiple Data Bytes

33.7.6

33.7.6.1

628

TXCOMP

RXRDY

TWD

SAM3U Series

Internal Address

S

7-bit Slave Addressing

Write START Bit

DADR

RXRDY is used as Receive Ready for the PDC receive channel.

The TWI interface can perform various transfer formats: Transfers with 7-bit slave address

devices and 10-bit slave address devices.

When Addressing 7-bit slave devices, the internal address bytes are used to perform random

address (read or write) accesses to reach one or more data bytes, within a memory page loca-

tion in a serial memory, for example. When performing read operations with an internal address,

the TWI performs a write operation to set the internal address into the slave device, and then

switch to Master Receiver mode. Note that the second start condition (after sending the IADR) is

sometimes called “repeated start” (Sr) in I2C fully-compatible devices. See

Figure 33-11

The three internal address bytes are configurable through the Master Mode register

(TWI_MMR).

If the slave device supports only a 7-bit address, i.e. no internal address, IADRSZ must be set

to 0.

In the figures below the following abbreviations are used:

• S

• Sr

• P

• W

• R

• A

• N

• DADR

• IADR

R

A

and

Start

Repeated Start

Stop

Write

Read

Acknowledge

Not Acknowledge

Device Address

Internal Address

DATA n

Figure 33-13

Read RHR

A

DATA n

for Master Write operation with internal address.

DATA (n+1)

A

DATA (n+1)

Read RHR

DATA (n+m)-1

DATA (n+m)-1

A

Read RHR

after next-to-last data read

DATA (n+m)

Write STOP Bit

6430D–ATARM–25-Mar-11

Figure

N

33-12. See

DATA (n+m)

Read RHR

P

Related parts for ATSAM3U4CA-CU

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT EVAL FOR AT91SAM3U CORTEX

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

AT91 ARM Thumb-based Microcontrollers

Manufacturer:

ATMEL [ATMEL Corporation]

Datasheet:

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Monolithic Integrated Feature Phone Circuit

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Multistandard Video-IF and Quasi Parallel Sound Processing

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

High-performance EE PLD

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

8-bit Flash Microcontroller

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

2-Wire Serial EEPROM

Manufacturer:

ATMEL Corporation

Datasheet: