ATSAM3U4CA-CU Atmel, ATSAM3U4CA-CU Datasheet - Page 599

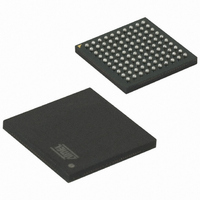

ATSAM3U4CA-CU

Manufacturer Part Number

ATSAM3U4CA-CU

Description

IC MCU 32BIT 256KB FLSH 100TFBGA

Manufacturer

Atmel

Series

SAM3Ur

Specifications of ATSAM3U4CA-CU

Core Processor

ARM® Cortex-M3™

Core Size

32-Bit

Speed

96MHz

Connectivity

EBI/EMI, I²C, MMC, SPI, SSC, UART/USART, USB

Peripherals

Brown-out Detect/Reset, DMA, I²S, POR, PWM, WDT

Number Of I /o

57

Program Memory Size

256KB (256K x 8)

Program Memory Type

FLASH

Ram Size

52K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 1.95 V

Data Converters

A/D 4x10b, 4x12b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-TFBGA

Processor Series

ATSAM3x

Core

ARM Cortex M3

Data Bus Width

32 bit

Data Ram Size

52 KB

Interface Type

3xUSART, TWI, 4xSPI, Bus

Maximum Clock Frequency

96 MHz

Number Of Programmable I/os

57

Number Of Timers

8

Operating Supply Voltage

1.62 V to 3.6 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

JTRACE-CM3, MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

ATSAM3U-EK

Minimum Operating Temperature

- 40 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

ATSAM3U4CA-CU

Manufacturer:

ATMEL/爱特梅尔

Quantity:

20 000

- Current page: 599 of 1171

- Download datasheet (25Mb)

Figure 32-9. Chip Select Decoding Application Block Diagram: Single Master/Multiple Slave Implementation

32.7.3.8

32.7.3.9

6430D–ATARM–25-Mar-11

6430D–ATARM–25-Mar-11

SPI Master

Peripheral Deselection without DMAC

Peripheral Deselection with DMAC

NPCS0

NPCS1

NPCS2

NPCS3

SPCK

MISO

MOSI

During a transfer of more than one data on a Chip Select without the DMAC, the SPI_TDR is

loaded by the processor, the flag TDRE rises as soon as the content of the SPI_TDR is trans-

ferred into the internal shift register. When this flag is detected high, the SPI_TDR can be

reloaded. If this reload by the processor occurs before the end of the current transfer and if the

next transfer is performed on the same chip select as the current transfer, the Chip Select is not

de-asserted between the two transfers. But depending on the application software handling the

SPI status register flags (by interrupt or polling method) or servicing other interrupts or other

tasks, the processor may not reload the SPI_TDR in time to keep the chip select active (low). A

null Delay Between Consecutive Transfer (DLYBCT) value in the SPI_CSR register, will give

even less time for the processor to reload the SPI_TDR. With some SPI slave peripherals,

requiring the chip select line to remain active (low) during a full set of transfers might lead to

communication errors.

To facilitate interfacing with such devices, the Chip Select Register [CSR0...CSR3] can be pro-

grammed with the CSAAT bit (Chip Select Active After Transfer) at 1. This allows the chip select

lines to remain in their current state (low = active) until transfer to another chip select is required.

Even if the SPI_TDR is not reloaded the chip select will remain active. To have the chip select

line to raise at the end of the transfer the Last transfer Bit (LASTXFER) in the SPI_MR register

must be set at 1 before writing the last data to transmit into the SPI_TDR.

When the Direct Memory Access Controller is used, the chip select line will remain low during

the whole transfer since the TDRE flag is managed by the DMAC itself. The reloading of the

SPI_TDR by the DMAC is done as soon as TDRE flag is set to one. In this case the use of

CSAAT bit might not be needed. However, it may happen that when other DMAC channels con-

1-of-n Decoder/Demultiplexer

SPCK

Slave 0

MISO MOSI

NSS

SPCK MISO MOSI

Slave 1

NSS

SAM3U Series

SAM3U Series

SPCK MISO MOSI

Slave 14

NSS

599

599

Related parts for ATSAM3U4CA-CU

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT EVAL FOR AT91SAM3U CORTEX

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

AT91 ARM Thumb-based Microcontrollers

Manufacturer:

ATMEL [ATMEL Corporation]

Datasheet:

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Monolithic Integrated Feature Phone Circuit

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Multistandard Video-IF and Quasi Parallel Sound Processing

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

High-performance EE PLD

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

8-bit Flash Microcontroller

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

2-Wire Serial EEPROM

Manufacturer:

ATMEL Corporation

Datasheet: