ATSAM3U4CA-CU Atmel, ATSAM3U4CA-CU Datasheet - Page 1157

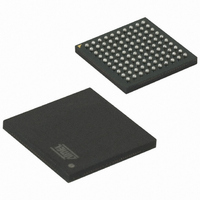

ATSAM3U4CA-CU

Manufacturer Part Number

ATSAM3U4CA-CU

Description

IC MCU 32BIT 256KB FLSH 100TFBGA

Manufacturer

Atmel

Series

SAM3Ur

Specifications of ATSAM3U4CA-CU

Core Processor

ARM® Cortex-M3™

Core Size

32-Bit

Speed

96MHz

Connectivity

EBI/EMI, I²C, MMC, SPI, SSC, UART/USART, USB

Peripherals

Brown-out Detect/Reset, DMA, I²S, POR, PWM, WDT

Number Of I /o

57

Program Memory Size

256KB (256K x 8)

Program Memory Type

FLASH

Ram Size

52K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 1.95 V

Data Converters

A/D 4x10b, 4x12b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-TFBGA

Processor Series

ATSAM3x

Core

ARM Cortex M3

Data Bus Width

32 bit

Data Ram Size

52 KB

Interface Type

3xUSART, TWI, 4xSPI, Bus

Maximum Clock Frequency

96 MHz

Number Of Programmable I/os

57

Number Of Timers

8

Operating Supply Voltage

1.62 V to 3.6 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

JTRACE-CM3, MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

ATSAM3U-EK

Minimum Operating Temperature

- 40 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

ATSAM3U4CA-CU

Manufacturer:

ATMEL/爱特梅尔

Quantity:

20 000

- Current page: 1157 of 1171

- Download datasheet (25Mb)

6430D–ATARM–25-Mar-11

Doc Rev

6430B

Comments

Introduction:

Section 1. ”SAM3U

2x TWIs (SAM3U1C/2C/4C have 1), up to 5x SPIs SAM3U1C/2C/4C have 4),

Table 1-1, “Configuration Summary”

SAM3U4/3/2C rows FWUP replaces NO in FWUP,SHDN pins column.

Figure 2-1 ”144-pin SAM3U4/2/1E Block Diagram”

updated, SM cell removed; UART moved to peripheral area, added Flash Unique block, removed 12B from

ADC block, added SysTick counter and Fmax 96MHz to M3 block. FWUP replaces WKUP in fig 2-1, FWUP

added to fig 2-2.

Figure 2-2 ”100-pin SAM3U4/2/1C Block

Table 3-1, “Signal Description

details given in footnote.

VDDIN, VDDOUT added to table.

”Serial Wire/JTAG Debug Port (SWJ-DP)”

status of pulldowns and pullups specified.

Section 4. ”Package and

Section 4.1 ”SAM3U4/2/1E Package and

finalized in datasheet.

Section 5.5.1 ”Backup

Figure 5-4 ”Wake-up

Table 5-1, “Low Power Mode Configuration

“Previous state saved.”

Figure 5-3 ”Backup Batteries

Section 6.6 ”NRSTB

Section 6. ”Input/Output Lines”

Section 6.1 ”General Purpose I/O Lines (GPIO)”

Line Considerations”.

Figure 6-1 ”On-Die Termination

Section 6.8 “PIO Controllers”, removed.

Section 8. ”Product

Section 9.

Memories”

Section 9.1.3.5 ”Security Bit

Table 7-3, “SAM3U Master to Slave

Section 7.2 ”APB/AHB

Table 11-3, “Multiplexing on PIO Controller B (PIOB)”

Section 12.10.1 ”12-bit High Speed

“Quadrature Decoder Logic” on page 51

Section 12.10.1 ”12-bit High Speed

Section 12.10.2 ”10-bit Low Power

ADC12B:

Section 41.6.6 ”ADC12B Analog Control

”Memories”; now comprises

.

Description”, Updated: 52 Kbytes of SRAM. 4x USARTs (SAM3U1C/2C/4C have 3), up to

Mapping”, title changed from “Memories”.

Pin”, VDDIO changed to VDDBU

Source”, BODEN replaced by SMEN. FWUP → Falling Edge Detector.

Mode”, BOD replaced by Supply Monitor/SM.

Bridges”, reference to ADC updated “10-bit ADC, 12-bit ADC (ADC12B)”.

Pinout”; reorganized according to product.

Feature”, updated

Used”, FWUP replaces FWKUP.

List”, Schmit Trigger added

replaces Section 5.8 “Programmable I/O Lines”.

schematic”, added.

ADC”, Ksample values updated on 2nd item of list.

ADC”,

ADC”, 2nd item on list updated.

Access”, Slave 9, High Speed Peripheral Bridge line added.

EBI column updated, 8 bits for SAM3U1C/2C/4C

Section 9.1 ”Embedded Memories”

properly stated in list of TC functions.

Register”,IBCTL reasigned to fields 8 and 9

Diagram”, NWR1/NBS1, NXRP0, A0 removed from block diagram,

Pinout”,

replaced ICE and JTAG. This section of the table updated

Section 12.10.2 ”10-bit Low Power

Summary”, PIO state in Low Power Mode, backup mode is;

and

Section 4.2 ”SAM3U4/2/1C Package and

and

Section 6.2 ”System I/O Lines”

ADC12B2, ADC12B3 properly listed.

Figure 2-2 ”100-pin SAM3U4/2/1C Block Diagram”

”PIO Controller - PIOA - PIOB -

and

ADC”, titles changed.

Section 9.2 ”External

replace Section 6. “I/O

PIOC”. exception

Pinout”, pinouts

SAM3U Series

Change

Request

Ref.

6400

6642

6482/6642

rfo/

6480

rfo

6471/rfo

6607

rfo

6645

6642

6646

6481/rfo

6663

6397

rfo

6649

1157

Related parts for ATSAM3U4CA-CU

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT EVAL FOR AT91SAM3U CORTEX

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

AT91 ARM Thumb-based Microcontrollers

Manufacturer:

ATMEL [ATMEL Corporation]

Datasheet:

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Monolithic Integrated Feature Phone Circuit

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Multistandard Video-IF and Quasi Parallel Sound Processing

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

High-performance EE PLD

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

8-bit Flash Microcontroller

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

2-Wire Serial EEPROM

Manufacturer:

ATMEL Corporation

Datasheet: