ATSAM3U4CA-CU Atmel, ATSAM3U4CA-CU Datasheet - Page 1001

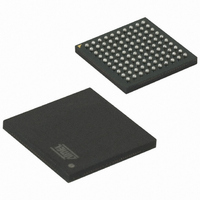

ATSAM3U4CA-CU

Manufacturer Part Number

ATSAM3U4CA-CU

Description

IC MCU 32BIT 256KB FLSH 100TFBGA

Manufacturer

Atmel

Series

SAM3Ur

Specifications of ATSAM3U4CA-CU

Core Processor

ARM® Cortex-M3™

Core Size

32-Bit

Speed

96MHz

Connectivity

EBI/EMI, I²C, MMC, SPI, SSC, UART/USART, USB

Peripherals

Brown-out Detect/Reset, DMA, I²S, POR, PWM, WDT

Number Of I /o

57

Program Memory Size

256KB (256K x 8)

Program Memory Type

FLASH

Ram Size

52K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 1.95 V

Data Converters

A/D 4x10b, 4x12b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-TFBGA

Processor Series

ATSAM3x

Core

ARM Cortex M3

Data Bus Width

32 bit

Data Ram Size

52 KB

Interface Type

3xUSART, TWI, 4xSPI, Bus

Maximum Clock Frequency

96 MHz

Number Of Programmable I/os

57

Number Of Timers

8

Operating Supply Voltage

1.62 V to 3.6 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

JTRACE-CM3, MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

ATSAM3U-EK

Minimum Operating Temperature

- 40 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

ATSAM3U4CA-CU

Manufacturer:

ATMEL/爱特梅尔

Quantity:

20 000

- Current page: 1001 of 1171

- Download datasheet (25Mb)

Notes:

If this bit is reset, then the user should consider that a new n-transaction is coming.

This bit is reset by UDPHS_EPTRST register EPT_x (reset endpoint), and by UDPHS_EPTCTLDISx (disable endpoint).

• RX_SETUP/ERR_FL_ISO: Received SETUP/Error Flow

This bit is set by hardware when a valid SETUP packet has been received from the host.

It is cleared by the device firmware after reading the SETUP data from the endpoint FIFO.

This bit is reset by UDPHS_EPTRST register EPT_x (reset endpoint), and by UDPHS_EPTCTLDISx (disable endpoint).

This bit is set by hardware when a transaction error occurs.

This bit is reset by UDPHS_EPTRST register EPT_x (reset endpoint) and by UDPHS_EPTCTLDISx (disable endpoint).

• STALL_SNT/ERR_CRISO/ERR_NBTRA: Stall Sent/CRC ISO Error/Number of Transaction Error

This bit is set by hardware after a STALL handshake has been sent as requested by the UDPHS_EPTSTAx register

FRCESTALL bit.

This bit is reset by UDPHS_EPTRST register EPT_x (reset endpoint) and by UDPHS_EPTCTLDISx (disable endpoint).

This bit is set by hardware if the last received data is corrupted (CRC error on data).

This bit is updated by hardware when new data is received (Received OUT Data bit).

This bit is set at the end of a microframe in which at least one data bank has been transmitted, if less than the number of

transactions per micro-frame banks (UDPHS_EPTCFGx register NB_TRANS) have been validated for transmission inside

this microframe.

This bit is reset by UDPHS_EPTRST register EPT_x (reset endpoint) and by UDPHS_EPTCTLDISx (disable endpoint).

• NAK_IN/ERR_FLUSH: NAK IN/Bank Flush Error

This bit is set by hardware when a NAK handshake has been sent in response to an IN request from the Host.

This bit is cleared by software.

This bit is set when flushing unsent banks at the end of a microframe.

This bit is reset by UDPHS_EPTRST register EPT_x (reset endpoint) and by EPT_CTL_DISx (disable endpoint).

6430D–ATARM–25-Mar-11

6430D–ATARM–25-Mar-11

– Received SETUP: (for Control endpoint only)

– Error Flow: (for isochronous endpoint only)

– Isochronous IN transaction is missed, the micro has no time to fill the endpoint (underflow).

– Isochronous OUT data is dropped because the bank is busy (overflow).

– STALL_SNT: (for Control, Bulk and Interrupt endpoints)

– ERR_CRISO: (for Isochronous OUT endpoints) (Read-only)

– ERR_NBTRA: (for High Bandwidth Isochronous IN endpoints)

– NAK_IN:

– ERR_FLUSH: (for High Bandwidth Isochronous IN endpoints)

1. A transaction error occurs when the toggle sequencing does not respect the Universal Serial Bus Specification, Rev 2.0

2. When a transaction error occurs, the user may empty all the “bad” transactions by clearing the Received OUT Data flag

(5.9.2 High Bandwidth Isochronous endpoints) (Bad PID, missing data....)

(RX_BK_RDY).

SAM3U Series

SAM3U Series

1001

1001

Related parts for ATSAM3U4CA-CU

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT EVAL FOR AT91SAM3U CORTEX

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

AT91 ARM Thumb-based Microcontrollers

Manufacturer:

ATMEL [ATMEL Corporation]

Datasheet:

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Monolithic Integrated Feature Phone Circuit

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Multistandard Video-IF and Quasi Parallel Sound Processing

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

High-performance EE PLD

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

8-bit Flash Microcontroller

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

2-Wire Serial EEPROM

Manufacturer:

ATMEL Corporation

Datasheet: