EP1S40B956C5 Altera, EP1S40B956C5 Datasheet - Page 795

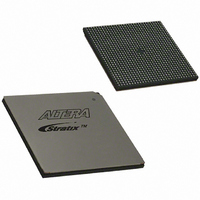

EP1S40B956C5

Manufacturer Part Number

EP1S40B956C5

Description

IC STRATIX FPGA 40K LE 956-BGA

Manufacturer

Altera

Series

Stratix®r

Datasheet

1.EP1S10F484I6N.pdf

(864 pages)

Specifications of EP1S40B956C5

Number Of Logic Elements/cells

41250

Number Of Labs/clbs

4125

Total Ram Bits

3423744

Number Of I /o

683

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

956-BGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

EP1S40B956C5

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

- Current page: 795 of 864

- Download datasheet (11Mb)

Altera Corporation

September 2004

Page select

Current

configuration

(AnF)

Illegal values

Table 12–8. Parameter Settings for the altremote_update Megafunction (Part 2 of 2)

Parameter

Selected

param[2..0]

bit setting

100

101

001

110

111

Remote Update WYSIWYG ATOM

An alternative to using the altremote_update megafunction is to

directly instantiate the remote update WYSIWYG atom. This atom should

be included in the factory configuration and any application

configuration image to access the remote configuration shift registers.

When implementing the atom, you should consider following:

1.

2.

3.

4.

parameter

width of

Only one atom can be used in the circuit; more than one gives a

no-fit.

All signals for the cell must be connected. The clock port (CLK) must

be connected to a live cell. The others can be constant V

The pgmout port must be connected and must feed PGM[2.0]

output pins (it cannot be connected to anything else but output

pins).

The Quartus II software reserves RUnLU as an input pin, and you

must connect it to V

value

3

1

Remote System Configuration with Stratix & Stratix GX Devices

3 bit '001' - Local

1 bit '0' - Factory Specifies whether the current configuration is

configuration

configuration

POR Reset

3 bit '000' -

Application

1 bit '1' -

Remote

Value

CC

.

Page mode selection. Writing of this parameter

is only allowed when in the factory

configuration.

factory or and application configuration. This

parameter can only be read.

Stratix Device Handbook, Volume 2

Description

CC

or GND.

12–17

Related parts for EP1S40B956C5

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: