EP1S40B956C5 Altera, EP1S40B956C5 Datasheet - Page 369

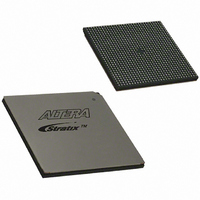

EP1S40B956C5

Manufacturer Part Number

EP1S40B956C5

Description

IC STRATIX FPGA 40K LE 956-BGA

Manufacturer

Altera

Series

Stratix®r

Datasheet

1.EP1S10F484I6N.pdf

(864 pages)

Specifications of EP1S40B956C5

Number Of Logic Elements/cells

41250

Number Of Labs/clbs

4125

Total Ram Bits

3423744

Number Of I /o

683

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

956-BGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

EP1S40B956C5

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

- Current page: 369 of 864

- Download datasheet (11Mb)

Introduction

TriMatrix

Memory

Altera Corporation

July 2005

S52003-3.3

f

Stratix and Stratix GX devices feature the TriMatrix™ memory

structure, composed of three sizes of embedded RAM blocks. TriMatrix

memory includes 512-bit M512 blocks, 4-Kbit M4K blocks, and 512-Kbit

M-RAM blocks, each of which is configurable to support a wide range of

features. Offering up to 10 Mbits of RAM and up to 12 terabits per second

of device memory bandwidth, the TriMatrix memory structure makes the

Stratix and Stratix GX families ideal for memory-intensive applications.

TriMatrix memory structures can implement a wide variety of complex

memory functions. For example, use the small M512 blocks for first-in

first-out (FIFO) functions and clock domain buffering where memory

bandwidth is critical. The M4K blocks are an ideal size for applications

requiring medium-sized memory, such as asynchronous transfer mode

(ATM) cell processing. M-RAM blocks enhance programmable logic

device (PLD) memory capabilities for large buffering applications, such

as internet protocol (IP) packet buffering and system cache.

TriMatrix memory blocks support various memory configurations,

including single-port, simple dual-port, true dual-port (also known as

bidirectional dual-port), shift-register, ROM, and FIFO mode. The

TriMatrix memory architecture also includes advanced features and

capabilities, such as byte enable support, parity-bit support, and mixed-

port width support. This chapter describes the various TriMatrix memory

modes and features.

Table 2–1

TriMatrix memory.

For more information on selecting which memory block to use, see

AN 207: TriMatrix Memory Selection Using the Quartus II Software.

summarizes the features supported by the three sizes of

Stratix & Stratix GX Devices

2. TriMatrix Embedded

Memory Blocks in

2–1

Related parts for EP1S40B956C5

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: