EP1S40B956C5 Altera, EP1S40B956C5 Datasheet - Page 663

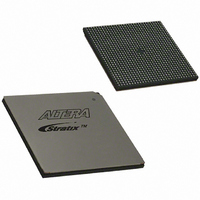

EP1S40B956C5

Manufacturer Part Number

EP1S40B956C5

Description

IC STRATIX FPGA 40K LE 956-BGA

Manufacturer

Altera

Series

Stratix®r

Datasheet

1.EP1S10F484I6N.pdf

(864 pages)

Specifications of EP1S40B956C5

Number Of Logic Elements/cells

41250

Number Of Labs/clbs

4125

Total Ram Bits

3423744

Number Of I /o

683

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

956-BGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

EP1S40B956C5

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

- Current page: 663 of 864

- Download datasheet (11Mb)

Altera Corporation

July 2005

Timing

XGMII signals must meet the timing requirements shown in

Make all XGMII timing measurements at the driver output (shown in

Figure

specified relative to the V

Figure 8–14. XGMII Timing Diagram

Table 8–8

Stratix and Stratix GX devices support DDR data with clock rates of up to

200 MHz, well above the XGMII clock rate of 156.25 MHz. For the HSTL

Class I I/O standard, Stratix and Stratix GX device I/O drivers provide a

1.0-V/ns slew rate at the input buffer of the receiving device.

XAUI

XAUI (pronounced Zowie) is located between the XGMII at the

reconciliation sublayer and the XGMII at the PHY layer.

shows the location of XAUI. XAUI is designed to either extend or replace

XGMII in chip-to-chip applications of most Ethernet MAC to PHY

interconnects.

Note to

(1)

T

T

Table 8–8. XGMII Timing Specifications

setup

hold

RXC, RXD

TXC, TXD,

RX_CLK

The actual set-up and hold times will be made available after device

characterization is complete.

TX_CLK

Symbol

Implementing 10-Gigabit Ethernet Using Stratix & Stratix GX Devices

8–14) and a capacitive load from all sources of 20 pF that are

Table

shows the XGMII timing specifications.

t

setup

8–8:

Driver

IL

960

960

_AC(max) and V

t

hold

Note (1)

Stratix Device Handbook, Volume 2

t

setup

Receiver

480

480

IH

_AC(min) thresholds.

Figure 8–15

t

hold

V

V

Figure

V

V

IL

IH

IL

IH

_AC(max)

Unit

_AC(max)

_AC(min)

_AC(min)

ps

ps

8–14.

8–19

Related parts for EP1S40B956C5

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: