DF2266TF13V Renesas Electronics America, DF2266TF13V Datasheet - Page 166

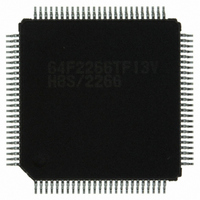

DF2266TF13V

Manufacturer Part Number

DF2266TF13V

Description

IC H8S/2266 MCU FLASH 100-TQFP

Manufacturer

Renesas Electronics America

Series

H8® H8S/2200r

Datasheet

1.DF2266TF20V.pdf

(712 pages)

Specifications of DF2266TF13V

Core Processor

H8S/2000

Core Size

16-Bit

Speed

13MHz

Connectivity

I²C, SCI, SmartCard

Peripherals

LCD, POR, PWM, WDT

Number Of I /o

67

Program Memory Size

128KB (128K x 8)

Program Memory Type

FLASH

Ram Size

8K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Data Converters

A/D 10x10b

Oscillator Type

Internal

Operating Temperature

-20°C ~ 75°C

Package / Case

100-TQFP, 100-VQFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

- Current page: 166 of 712

- Download datasheet (5Mb)

Section 7 Bus Controller

7.2.2

Even if a bus request is received from a bus master with a higher priority than that of the bus

master that has acquired the bus and is currently operating, the bus is not necessarily transferred

immediately. The CPU is the lowest-priority bus master, and if a bus request is received from the

DTC, the bus arbiter transfers the bus to the bus master that issued the request. The timing for

transfer of the bus is as follows:

• The bus is transferred at a break between bus cycles. However, if a bus cycle is executed in

• If the CPU is in sleep mode, it transfers the bus immediately.

The DTC sends the bus arbiter a request for the bus when an activation request is generated.

7.2.3

In a reset, the H8S/2268, including the bus controller, enters the reset state at that point, and an

executing bus cycle is discontinued.

Rev. 5.00 Sep. 01, 2009 Page 114 of 656

REJ09B0071-0500

discrete operations, as in the case of a longword-size access, the bus is not transferred between

such operations. For details, refer to section 2.7, Bus States During Instruction Execution, in

the H8S/2600 Series, H8S/2000 Series Programming Manual.

Bus Transfer Timing

Resets and the Bus Controller

Related parts for DF2266TF13V

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CONN SOCKET 2POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 4POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 5POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 3POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 5POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 2POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 3POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN SOCKET 4POS 7.92MM WHITE

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN HEADER 2POS 7.92MM R/A TIN

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

CONN HEADER 4POS 7.92MM R/A TIN

Manufacturer:

Hirose Electric Co Ltd

Datasheet:

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet: