C8051F902-GM Silicon Laboratories Inc, C8051F902-GM Datasheet - Page 197

C8051F902-GM

Manufacturer Part Number

C8051F902-GM

Description

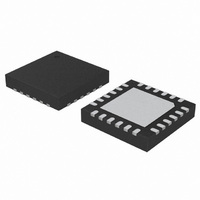

IC MCU 8BIT 8KB FLASH 24QFN

Manufacturer

Silicon Laboratories Inc

Series

C8051F9xxr

Specifications of C8051F902-GM

Program Memory Type

FLASH

Program Memory Size

8KB (8K x 8)

Package / Case

24-QFN

Core Processor

8051

Core Size

8-Bit

Speed

25MHz

Connectivity

SMBus (2-Wire/I²C), SPI, UART/USART

Peripherals

Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT

Number Of I /o

16

Ram Size

768 x 8

Voltage - Supply (vcc/vdd)

0.9 V ~ 3.6 V

Data Converters

A/D 15x10/12b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Processor Series

C8051F9x

Core

8051

Data Ram Size

768 B

Interface Type

UART

Maximum Clock Frequency

25 MHz

Number Of Timers

4

Operating Supply Voltage

0.9 V to 3.6 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

PK51, CA51, A51, ULINK2

Development Tools By Supplier

C8051F912DK

Minimum Operating Temperature

- 40 C

On-chip Adc

12 bit

Package

24QFN EP

Device Core

8051

Family Name

C8051F90x

Maximum Speed

25 MHz

Data Bus Width

8 Bit

Number Of Programmable I/os

16

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

336-1848-5

- Current page: 197 of 318

- Download datasheet (3Mb)

20.2.5. Automatic Gain Control (Crystal Mode Only) and SmaRTClock Bias Doubling

Automatic Gain Control allows the SmaRTClock oscillator to trim the oscillation amplitude of a crystal in

order to achieve the lowest possible power consumption. Automatic Gain Control automatically detects

when the oscillation amplitude has reached a point where it safe to reduce the drive current, therefore, it

may be enabled during crystal startup. It is recommended to enable Automatic Gain Control in most

systems which use the SmaRTClock oscillator in Crystal Mode. The following are recommended crystal

specifications and operating conditions when Automatic Gain Control is enabled:

•

•

•

•

When using Automatic Gain Control, it is recommended to perform an oscillation robustness test to ensure

that the chosen crystal will oscillate under the worst case condition to which the system will be exposed.

The worst case condition that should result in the least robust oscillation is at the following system

conditions: lowest temperature, highest supply voltage, highest ESR, highest load capacitance, and lowest

bias current (AGC enabled, Bias Double Disabled).

To perform the oscillation robustness test, the SmaRTClock oscillator should be enabled and selected as

the system clock source. Next, the SYSCLK signal should be routed to a port pin configured as a push-pull

digital output. The positive duty cycle of the output clock can be used as an indicator of oscillation

robustness. As shown in Figure 20.2, duty cycles less than 55% indicate a robust oscillation. As the duty

cycle approaches 60%, oscillation becomes less reliable and the risk of clock failure increases. Increasing

the bias current (by disabling AGC) will always improve oscillation robustness and will reduce the output

clock’s duty cycle. This test should be performed at the worst case system conditions, as results at very

low temperatures or high supply voltage will vary from results taken at room temperature or low supply

voltage.

As an alternative to performing the oscillation robustness test, Automatic Gain Control may be disabled at

the cost of increased power consumption (approximately 200 nA). Disabling Automatic Gain Control will

provide the crystal oscillator with higher immunity against external factors which may lead to clock failure.

Automatic Gain Control must be disabled if using the SmaRTClock oscillator in self-oscillate mode.

Table 20.3 shows a summary of the oscillator bias settings. The SmaRTClock Bias Doubling feature allows

the self-oscillation frequency to be increased (almost doubled) and allows a higher crystal drive strength in

crystal mode. High crystal drive strength is recommended when the crystal is exposed to poor

environmental conditions such as excessive moisture. SmaRTClock Bias Doubling is enabled by setting

BIASX2 (RTC0XCN.5) to 1.

ESR < 50 k

Load Capacitance < 10 pF

Supply Voltage < 3.0 V

Temperature > –20 °C

Figure 20.2. Interpreting Oscillation Robustness (Duty Cycle) Test Results

25%

Safe Operating Zone

55%

Low Risk of Clock

Rev. 1.0

Failure

C8051F91x-C8051F90x

60%

High Risk of Clock

Failure

Duty Cycle

197

Related parts for C8051F902-GM

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

SMD/C°/SINGLE-ENDED OUTPUT SILICON OSCILLATOR

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 AES KEYFOB DEMO WITH LCD RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 SIMPLIFIED KEY FOB DEMO WITH LED RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A/-40 TO 85 OC/EZLINK MODULE; F930/4432 HIGH BAND (REV E/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

EZLink Module; F930/4432 Low Band (rev e/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4460 10 DBM RADIO TEST CARD 434 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4461 14 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RFSWITCH RADIO TEST CARD 460 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 27 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 SKYWORKS 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

N/A N/A/-40 TO 85 OC/4463 RFMD 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 169 MHZ

Manufacturer:

Silicon Laboratories Inc