MA180023 Microchip Technology, MA180023 Datasheet - Page 57

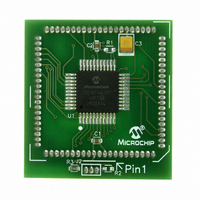

MA180023

Manufacturer Part Number

MA180023

Description

MODULE PLUG-IN PIC18F46J11 PIM

Manufacturer

Microchip Technology

Series

PIC®r

Datasheet

1.MA180023.pdf

(528 pages)

Specifications of MA180023

Accessory Type

Plug-In Module (PIM) - PIC18F46J11

Tool / Board Applications

General Purpose MCU, MPU, DSP, DSC

Mcu Supported Families

PIC18

Supported Devices

Stand-alone Or W/ HPC(DM183022) Or PIC18(DM183032)

Silicon Manufacturer

Microchip

Core Architecture

PIC

Core Sub-architecture

PIC18

Silicon Core Number

PIC18F

Silicon Family Name

PIC18FxxJxx

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With/related Products

HPC Explorer Board (DM183022) or PIC18 Explorer Board (DM183032)

For Use With

DM183032 - BOARD EXPLORER PICDEM PIC18DM183022 - BOARD DEMO PIC18FXX22 64/80TQFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MA180023

Manufacturer:

Microchip Technology

Quantity:

135

- Current page: 57 of 528

- Download datasheet (8Mb)

4.0

The PIC18F46J11 family of devices differentiates

among various kinds of Reset:

a)

b)

c)

d)

e)

f)

g)

h)

i)

j)

This section discusses Resets generated by MCLR,

POR and BOR, and covers the operation of the various

start-up timers.

For information on WDT Resets, see Section 25.2

“Watchdog Timer (WDT)”. For Stack Reset events,

see Section 5.1.4.4 “Stack Full and Underflow

Resets” and for Deep Sleep mode, see Section 3.6

“Deep Sleep Mode”.

FIGURE 4-1:

© 2009 Microchip Technology Inc.

Power-on Reset (POR)

MCLR Reset during normal operation

MCLR Reset during power-managed modes

Watchdog

execution)

Configuration Mismatch (CM)

Brown-out Reset (BOR)

RESET Instruction

Stack Full Reset

Stack Underflow Reset

Deep Sleep Reset

MCLR

Note 1: The Brown-out Reset is not available in PIC18LF2XJ11 and PIC18LF4XJ11 devices.

V

DD

RESET

Deep Sleep Reset

Pointer

Stack

Configuration Word Mismatch

PWRT

Timer

Brown-out

INTRC

( )_IDLE

V

Time-out

32 ms

Reset

DD

Detect

WDT

Sleep

Rise

External Reset

SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

Stack Full/Underflow Reset

(1)

RESET Instruction

(WDT)

POR Pulse

PWRT

11-Bit Ripple Counter

Reset

66 ms

(during

PIC18F46J11 FAMILY

Figure 4-1 provides a simplified block diagram of the

on-chip Reset circuit.

4.1

Device Reset events are tracked through the RCON

register (Register 4-1). The lower five bits of the register

indicate that a specific Reset event has occurred. In

most cases, these bits can only be set by the event and

must be cleared by the application after the event. The

state of these flag bits, taken together, can be read to

indicate the type of Reset that just occurred. This is

described in more detail in Section 4.7 “Reset State of

Registers”.

The ECON register also has a control bit for setting

interrupt priority (IPEN). Interrupt priority is discussed

in Section 8.0 “Interrupts”.

RCON Register

S

R

Q

DS39932C-page 57

Chip_Reset

Related parts for MA180023

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet: