MA180023 Microchip Technology, MA180023 Datasheet - Page 144

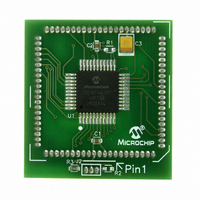

MA180023

Manufacturer Part Number

MA180023

Description

MODULE PLUG-IN PIC18F46J11 PIM

Manufacturer

Microchip Technology

Series

PIC®r

Datasheet

1.MA180023.pdf

(528 pages)

Specifications of MA180023

Accessory Type

Plug-In Module (PIM) - PIC18F46J11

Tool / Board Applications

General Purpose MCU, MPU, DSP, DSC

Mcu Supported Families

PIC18

Supported Devices

Stand-alone Or W/ HPC(DM183022) Or PIC18(DM183032)

Silicon Manufacturer

Microchip

Core Architecture

PIC

Core Sub-architecture

PIC18

Silicon Core Number

PIC18F

Silicon Family Name

PIC18FxxJxx

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With/related Products

HPC Explorer Board (DM183022) or PIC18 Explorer Board (DM183032)

For Use With

DM183032 - BOARD EXPLORER PICDEM PIC18DM183022 - BOARD DEMO PIC18FXX22 64/80TQFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MA180023

Manufacturer:

Microchip Technology

Quantity:

135

- Current page: 144 of 528

- Download datasheet (8Mb)

available on a particular device, users can better tailor

PIC18F46J11 FAMILY

9.7

A major challenge in general purpose devices is provid-

ing the largest possible set of peripheral features while

minimizing the conflict of features on I/O pins. The

challenge is even greater on low pin count devices

similar to the PIC18F46J11 family. In an application

that needs to use more than one peripheral multiplexed

on single pin, inconvenient workarounds in application

code or a complete redesign may be the only option.

The Peripheral Pin Select (PPS) feature provides an

alternative to these choices by enabling the user’s

peripheral set selection and their placement on a wide

range of I/O pins. By increasing the pinout options

the microcontroller to their entire application, rather than

trimming the application to fit the device.

The PPS feature operates over a fixed subset of digital

I/O pins. Users may independently map the input and/

or output of any one of the many digital peripherals to

any one of these I/O pins. PPS is performed in software

and generally does not require the device to be

reprogrammed. Hardware safeguards are included that

prevent accidental or spurious changes to the

peripheral mapping once it has been established.

9.7.1

The PPS feature is used with a range of up to 22 pins;

the number of available pins is dependent on the

particular device and its pin count. Pins that support the

PPS feature include the designation “RPn” in their full

pin designation, where “RP” designates a remappable

peripheral and “n” is the remappable pin number. See

Table 1-2 for pinout options in each package offering.

DS39932C-page 144

Peripheral Pin Select (PPS)

AVAILABLE PINS

Priority is given regardless of the type of peripheral that

9.7.2

The peripherals managed by the PPS are all digital

only peripherals. These include general serial commu-

nications (UART and SPI), general purpose timer clock

inputs, timer-related peripherals (input capture and

output compare) and external interrupt inputs. Also

included are the outputs of the comparator module,

since these are discrete digital signals.

The PPS module is not applied to I

tion inputs, RTCC alarm outputs or peripherals with

analog inputs. Additionally, the MSSP1 and EUSART1

modules are not routed through the PPS module.

A key difference between pin select and non-pin select

peripherals is that pin select peripherals are not asso-

ciated with a default I/O pin. The peripheral must

always be assigned to a specific I/O pin before it can be

used. In contrast, non PPS peripherals are always

available on a default pin, assuming that the peripheral

is active and not conflicting with another peripheral.

9.7.2.1

When a pin selectable peripheral is active on a given I/O

pin, it takes priority over all other digital I/O and digital

communication peripherals associated with the pin.

is mapped. Pin select peripherals never take priority

over any analog functions associated with the pin.

9.7.3

PPS features are controlled through two sets of Special

Function Registers (SFRs): one to map peripheral

inputs and the other to map outputs. Because they are

separately controlled, a particular peripheral’s input

and output (if the peripheral has both) can be placed on

any selectable function pin without constraint.

The association of a peripheral to a peripheral selectable

pin is handled in two different ways, depending on

whether an input or an output is being mapped.

AVAILABLE PERIPHERALS

CONTROLLING PERIPHERAL PIN

SELECT

Peripheral Pin Select Function

Priority

© 2009 Microchip Technology Inc.

2

C, change notifica-

Related parts for MA180023

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet: