MA180023 Microchip Technology, MA180023 Datasheet - Page 111

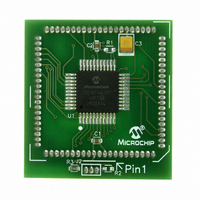

MA180023

Manufacturer Part Number

MA180023

Description

MODULE PLUG-IN PIC18F46J11 PIM

Manufacturer

Microchip Technology

Series

PIC®r

Datasheet

1.MA180023.pdf

(528 pages)

Specifications of MA180023

Accessory Type

Plug-In Module (PIM) - PIC18F46J11

Tool / Board Applications

General Purpose MCU, MPU, DSP, DSC

Mcu Supported Families

PIC18

Supported Devices

Stand-alone Or W/ HPC(DM183022) Or PIC18(DM183032)

Silicon Manufacturer

Microchip

Core Architecture

PIC

Core Sub-architecture

PIC18

Silicon Core Number

PIC18F

Silicon Family Name

PIC18FxxJxx

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With/related Products

HPC Explorer Board (DM183022) or PIC18 Explorer Board (DM183032)

For Use With

DM183032 - BOARD EXPLORER PICDEM PIC18DM183022 - BOARD DEMO PIC18FXX22 64/80TQFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MA180023

Manufacturer:

Microchip Technology

Quantity:

135

- Current page: 111 of 528

- Download datasheet (8Mb)

8.1

The INTCON registers are readable and writable

registers, which contain various enable, priority and

flag bits.

REGISTER 8-1:

© 2009 Microchip Technology Inc.

bit 7

Legend:

R = Readable bit

-n = Value at POR

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0

Note 1:

GIE/GIEH

R/W-0

INTCON Registers

A mismatch condition will continue to set this bit. Reading PORTB and waiting 1 T

condition and allow the bit to be cleared.

GIE/GIEH: Global Interrupt Enable bit

When IPEN = 0:

1 = Enables all unmasked interrupts

0 = Disables all interrupts

When IPEN = 1:

1 = Enables all high-priority interrupts

0 = Disables all interrupts

PEIE/GIEL: Peripheral Interrupt Enable bit

When IPEN = 0:

1 = Enables all unmasked peripheral interrupts

0 = Disables all peripheral interrupts

When IPEN = 1:

1 = Enables all low-priority peripheral interrupts

0 = Disables all low-priority peripheral interrupts

TMR0IE: TMR0 Overflow Interrupt Enable bit

1 = Enables the TMR0 overflow interrupt

0 = Disables the TMR0 overflow interrupt

INT0IE: INT0 External Interrupt Enable bit

1 = Enables the INT0 external interrupt

0 = Disables the INT0 external interrupt

RBIE: RB Port Change Interrupt Enable bit

1 = Enables the RB port change interrupt

0 = Disables the RB port change interrupt

TMR0IF: TMR0 Overflow Interrupt Flag bit

1 = TMR0 register has overflowed (must be cleared in software)

0 = TMR0 register did not overflow

INT0IF: INT0 External Interrupt Flag bit

1 = The INT0 external interrupt occurred (must be cleared in software)

0 = The INT0 external interrupt did not occur

RBIF: RB Port Change Interrupt Flag bit

1 = At least one of the RB<7:4> pins changed state (must be cleared in software)

0 = None of the RB<7:4> pins have changed state

PEIE/GIEL

R/W-0

INTCON: INTERRUPT CONTROL REGISTER (ACCESS FF2h)

W = Writable bit

‘1’ = Bit is set

TMR0IE

R/W-0

INT0IE

R/W-0

(1)

U = Unimplemented bit, read as ‘0’

‘0’ = Bit is cleared

PIC18F46J11 FAMILY

R/W-0

RBIE

Note:

Interrupt flag bits are set when an interrupt

condition occurs regardless of the state of

its corresponding enable bit or the global

interrupt enable bit. User software should

ensure the appropriate interrupt flag bits

are clear prior to enabling an interrupt.

This feature allows for software polling.

TMR0IF

R/W-0

x = Bit is unknown

CY

INT0IF

R/W-0

will end the mismatch

DS39932C-page 111

RBIF

R/W-x

(1)

bit 0

Related parts for MA180023

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet: