MA180023 Microchip Technology, MA180023 Datasheet - Page 46

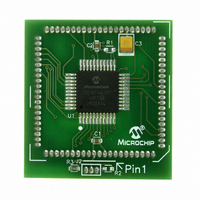

MA180023

Manufacturer Part Number

MA180023

Description

MODULE PLUG-IN PIC18F46J11 PIM

Manufacturer

Microchip Technology

Series

PIC®r

Datasheet

1.MA180023.pdf

(528 pages)

Specifications of MA180023

Accessory Type

Plug-In Module (PIM) - PIC18F46J11

Tool / Board Applications

General Purpose MCU, MPU, DSP, DSC

Mcu Supported Families

PIC18

Supported Devices

Stand-alone Or W/ HPC(DM183022) Or PIC18(DM183032)

Silicon Manufacturer

Microchip

Core Architecture

PIC

Core Sub-architecture

PIC18

Silicon Core Number

PIC18F

Silicon Family Name

PIC18FxxJxx

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With/related Products

HPC Explorer Board (DM183022) or PIC18 Explorer Board (DM183032)

For Use With

DM183032 - BOARD EXPLORER PICDEM PIC18DM183022 - BOARD DEMO PIC18FXX22 64/80TQFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MA180023

Manufacturer:

Microchip Technology

Quantity:

135

- Current page: 46 of 528

- Download datasheet (8Mb)

PIC18F46J11 FAMILY

3.4

The Idle modes allow the controller’s CPU to be

selectively shut down while the peripherals continue to

operate. Selecting a particular Idle mode allows users

to further manage power consumption.

If the IDLEN bit is set to ‘1’ when a SLEEP instruction is

executed, the peripherals will be clocked from the clock

source selected using the SCS<1:0> bits; however, the

CPU will not be clocked. The clock source status bits are

not affected. Setting IDLEN and executing a SLEEP

instruction provides a quick method of switching from a

given Run mode to its corresponding Idle mode.

If the WDT is selected, the INTRC source will continue

to operate. If the Timer1 oscillator is enabled, it will also

continue to run.

Since the CPU is not executing instructions, the only

exits from any of the Idle modes are by interrupt, WDT

time-out or a Reset. When a wake event occurs, CPU

execution is delayed by an interval of T

(parameter 38, Table 28-13) while it becomes ready to

execute code. When the CPU begins executing code,

it resumes with the same clock source for the current

Idle mode. For example, when waking from RC_IDLE

mode, the internal oscillator block will clock the CPU

and peripherals (in other words, RC_RUN mode). The

IDLEN and SCS bits are not affected by the wake-up.

While in any Idle or Sleep mode, a WDT time-out will

result in a WDT wake-up to the Run mode currently

specified by the SCS<1:0> bits.

3.4.1

This mode is unique among the three low-power Idle

modes, in that it does not disable the primary device

clock. For timing-sensitive applications, this allows for

the fastest resumption of device operation with its more

accurate primary clock source, since the clock source

does not have to “warm up” or transition from another

oscillator.

PRI_IDLE mode is entered from PRI_RUN mode by

setting the IDLEN bit and executing a SLEEP instruc-

tion. If the device is in another Run mode, set IDLEN

first, then set the SCS bits to ‘00’ and execute SLEEP.

Although the CPU is disabled, the peripherals continue

to be clocked from the primary clock source specified

by the FOSC<1:0> Configuration bits. The OSTS bit

remains set (see Figure 3-7).

DS39932C-page 46

Idle Modes

PRI_IDLE MODE

CSD

When a wake event occurs, the CPU is clocked from the

primary clock source. A delay of interval, T

required between the wake event and when code

execution starts. This is required to allow the CPU to

become ready to execute instructions. After the

wake-up, the OSTS bit remains set. The IDLEN and

SCS bits are not affected by the wake-up (see

Figure 3-8).

3.4.2

In SEC_IDLE mode, the CPU is disabled but the

peripherals continue to be clocked from the Timer1

oscillator. This mode is entered from SEC_RUN by set-

ting the IDLEN bit and executing a SLEEP instruction. If

the device is in another Run mode, set IDLEN first, then

set SCS<1:0> to ‘01’ and execute SLEEP. When the

clock source is switched to the Timer1 oscillator, the

primary oscillator is shut down, the OSTS bit is cleared

and the T1RUN bit is set.

When a wake event occurs, the peripherals continue to

be clocked from the Timer1 oscillator. After an interval

of T

cuting code being clocked by the Timer1 oscillator. The

IDLEN and SCS bits are not affected by the wake-up;

the Timer1 oscillator continues to run (see Figure 3-8).

Note:

CSD

following the wake event, the CPU begins exe-

SEC_IDLE MODE

The Timer1 oscillator should already be

running prior to entering SEC_IDLE mode.

If the T1OSCEN bit is not set when the

SLEEP instruction is executed, the SLEEP

instruction will be ignored and entry to

SEC_IDLE mode will not occur. If the

Timer1 oscillator is enabled, but not yet

running, peripheral clocks will be delayed

until the oscillator has started. In such

situations, initial oscillator operation is far

from stable and unpredictable operation

may result.

© 2009 Microchip Technology Inc.

CSD

, is

Related parts for MA180023

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet: