MA180023 Microchip Technology, MA180023 Datasheet - Page 323

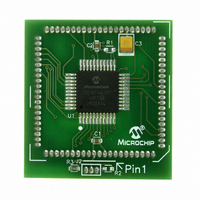

MA180023

Manufacturer Part Number

MA180023

Description

MODULE PLUG-IN PIC18F46J11 PIM

Manufacturer

Microchip Technology

Series

PIC®r

Datasheet

1.MA180023.pdf

(528 pages)

Specifications of MA180023

Accessory Type

Plug-In Module (PIM) - PIC18F46J11

Tool / Board Applications

General Purpose MCU, MPU, DSP, DSC

Mcu Supported Families

PIC18

Supported Devices

Stand-alone Or W/ HPC(DM183022) Or PIC18(DM183032)

Silicon Manufacturer

Microchip

Core Architecture

PIC

Core Sub-architecture

PIC18

Silicon Core Number

PIC18F

Silicon Family Name

PIC18FxxJxx

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With/related Products

HPC Explorer Board (DM183022) or PIC18 Explorer Board (DM183032)

For Use With

DM183032 - BOARD EXPLORER PICDEM PIC18DM183022 - BOARD DEMO PIC18FXX22 64/80TQFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MA180023

Manufacturer:

Microchip Technology

Quantity:

135

- Current page: 323 of 528

- Download datasheet (8Mb)

REGISTER 19-2:

© 2009 Microchip Technology Inc.

bit 7

Legend:

R = Readable bit

-n = Value at POR

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0

R/W-0

SPEN

SPEN: Serial Port Enable bit

1 = Serial port enabled (configures RXx/DTx and TXx/CKx pins as serial port pins)

0 = Serial port disabled (held in Reset)

RX9: 9-Bit Receive Enable bit

1 = Selects 9-bit reception

0 = Selects 8-bit reception

SREN: Single Receive Enable bit

Asynchronous mode:

Don’t care.

Synchronous mode – Master:

1 = Enables single receive

0 = Disables single receive

This bit is cleared after reception is complete.

Synchronous mode – Slave:

Don’t care.

CREN: Continuous Receive Enable bit

Asynchronous mode:

1 = Enables receiver

0 = Disables receiver

Synchronous mode:

1 = Enables continuous receive until enable bit, CREN, is cleared (CREN overrides SREN)

0 = Disables continuous receive

ADDEN: Address Detect Enable bit

Asynchronous mode 9-Bit (RX9 = 1):

1 = Enables address detection, enables interrupt and loads the receive buffer when RSR<8> is set

0 = Disables address detection, all bytes are received and ninth bit can be used as parity bit

Asynchronous mode 9-Bit (RX9 = 0):

Don’t care.

FERR: Framing Error bit

1 = Framing error (can be updated by reading RCREGx register and receiving next valid byte)

0 = No framing error

OERR: Overrun Error bit

1 = Overrun error (can be cleared by clearing bit CREN)

0 = No overrun error

RX9D: 9

This can be address/data bit or a parity bit and must be calculated by user firmware.

R/W-0

RX9

RCSTAx: RECEIVE STATUS AND CONTROL REGISTER (ACCESS FACh/F9Ch)

th

bit of Received Data

W = Writable bit

‘1’ = Bit is set

R/W-0

SREN

CREN

R/W-0

U = Unimplemented bit, read as ‘0’

‘0’ = Bit is cleared

PIC18F46J11 FAMILY

ADDEN

R/W-0

FERR

R-0

x = Bit is unknown

OERR

R-0

DS39932C-page 323

RX9D

R-x

bit 0

Related parts for MA180023

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet: