AT91SAM7XC512-CU Atmel, AT91SAM7XC512-CU Datasheet - Page 711

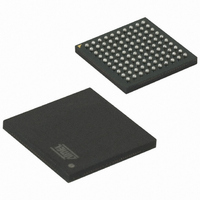

AT91SAM7XC512-CU

Manufacturer Part Number

AT91SAM7XC512-CU

Description

MCU ARM 512K HS FLASH 100-TFBGA

Manufacturer

Atmel

Series

AT91SAMr

Specifications of AT91SAM7XC512-CU

Core Processor

ARM7

Core Size

16/32-Bit

Speed

55MHz

Connectivity

CAN, Ethernet, I²C, SPI, SSC, UART/USART, USB

Peripherals

Brown-out Detect/Reset, DMA, POR, PWM, WDT

Number Of I /o

62

Program Memory Size

512KB (512K x 8)

Program Memory Type

FLASH

Ram Size

128K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 1.95 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-TFBGA

Processor Series

AT91SAMx

Core

ARM7TDMI

Data Bus Width

32 bit

Data Ram Size

128 KB

Interface Type

MII, SPI, TWI

Maximum Clock Frequency

55 MHz

Number Of Programmable I/os

62

Number Of Timers

3

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

JTRACE-ARM-2M, KSK-AT91SAM7X-PL, MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

AT91SAM-ICE, AT91-ISP, AT91SAM7XC-EK

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 8 Channel

For Use With

AT91SAM-ICE - EMULATOR FOR AT91 ARM7/ARM9AT91SAM7XC-EK - KIT EVAL FOR AT91SAM7XC256/128

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 711 of 727

- Download datasheet (11Mb)

6209F–ATARM–17-Feb-09

Version

6209E

,

(Continued) Comments

RSTC,

Section 13.2.4.4 ”Software

SPI,

Section 28.6.4 “SPI Slave Mode” on page

SPI_RDR.

SSC,

Section 30.6.5.1 ”Frame Sync

Section 30.6.6.1 ”Compare

Section 30.8.3 ”SSC Receive Clock Mode

TC,

Figure 32-2,”Clock Chaining

Section 32.6 ”Timer Counter (TC) User

one table.

Section 32.6.3 on page 410

value added where relevant.

Section 32.6.2 ”TC Block Mode

Section 32.6.4 ”TC Channel Mode Register: Capture

TWI,

“Two-wire Interface

Important changes to this datasheet include a clarification of Atmel TWI compatibility with I

UDP,

Table 34-2, “USB Communication

In the USB_CSR register, the control endpoints are not effected by the bit field,

Disable” on page 484

Updated: write 1 =.... in

Updated: write 0 = ....in

Section 34.6.10 “UDP Endpoint Control and Status Register” on page

instructions regarding USB clock and system clock cycle, and updated “note” appearing under the code. “wait 3

USB clock cycles and 3 system clock cycles before accessing DPR from RX_DATAx and TXPKTRDY bit fields,

ditto for RX_DATAx and TXPKTRDY bit field descriptions.”

Section 34.2 ”Block

Clock domain, UDPCK specified as 48 MHz clock used by 12 MHz domain, in peripheral clock requirements.

Section 34.6 ”USB Device Port (UDP) User

Section 34.6.6 ”UDP Interrupt Mask

Section 34.6 ”USB Device Port (UDP) User

Table 34-1, “USB Endpoint

Section 34.5.2.5 ”Transmit Data

Section 34.6.9 ”UDP Reset Endpoint

(TWI)”, section has been updated.

Diagram”, in the text below the block diagram, MCK specified as clock used by Master

“RX_DATA_BK0: Receive Data Bank 0”

“TXPKTRDY: Transmit Packet Ready”

Reset”, PERRST must be used with PROCRST, except for debug purposes.

Functions”, updated with max FSLEN length.

Description”, footnote added to Dual-Bank heading.

to

Selection”, added to

Data”, defined max Frame Sync Data length.

Section 32.6.13 on page

Register”, typo corrected in bit fields 2 and 3.

Cancellation”, added to datasheet

Flow”, Supported Endpoint column updated.

Register”, Bit 12 of UDP_IMR cannot be masked and is always read at 1.

Register”, added steps to clear endpoints.

Interface”, register mapping w/indexed register scheme, consolidated in

AT91SAM7XC512/256/128 Preliminary

267, corrected information on OVRES (SPI_SR) and data read in

Register”, Corrected bit name to STTDLY

Interface”, the register mapping table has been updated.

Interface”, reset value for UDP_RST_EP is 0x000_0000.

Section 32.5 ”Functional

Mode”, bit filed 15 updated.

424, register names updated w/indexed values, WAVE

bit field of USB_CSR register.

bit field of USB_CSR register.

480, update to code and added

Description”.

“EPEDS: Endpoint Enable

2

C Standard.

Change

Request

Ref.

5436

3943

2293

4773

3342

4583

4247

3476

4063

4099

4462

4487

4508

4802

5049

5150

711

Related parts for AT91SAM7XC512-CU

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT EVAL FOR AT91SAM7XC256/128

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

KIT EVAL FOR AT91SAM7X256/128

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools KICKSTART KIT ATMEL AT91SAM7X

Manufacturer:

IAR Systems

Part Number:

Description:

MCU ARM9 64K SRAM 144-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM7 MCU FLASH 256K 100LQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MPU 217-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM9 ULTRA LOW PWR 217-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM9 324-TFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC MCU ARM9 SAMPLING 217CBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MCU 217-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MCU 208-PQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM 512K HS FLASH 100-LQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM 512K HS FLASH 100-TFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MCU 200 MHZ 324-TFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM MCU 16BIT 128K 256BGA

Manufacturer:

Atmel

Datasheet: