AT91SAM7XC512-CU Atmel, AT91SAM7XC512-CU Datasheet - Page 529

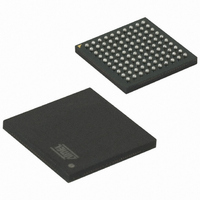

AT91SAM7XC512-CU

Manufacturer Part Number

AT91SAM7XC512-CU

Description

MCU ARM 512K HS FLASH 100-TFBGA

Manufacturer

Atmel

Series

AT91SAMr

Specifications of AT91SAM7XC512-CU

Core Processor

ARM7

Core Size

16/32-Bit

Speed

55MHz

Connectivity

CAN, Ethernet, I²C, SPI, SSC, UART/USART, USB

Peripherals

Brown-out Detect/Reset, DMA, POR, PWM, WDT

Number Of I /o

62

Program Memory Size

512KB (512K x 8)

Program Memory Type

FLASH

Ram Size

128K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 1.95 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-TFBGA

Processor Series

AT91SAMx

Core

ARM7TDMI

Data Bus Width

32 bit

Data Ram Size

128 KB

Interface Type

MII, SPI, TWI

Maximum Clock Frequency

55 MHz

Number Of Programmable I/os

62

Number Of Timers

3

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

JTRACE-ARM-2M, KSK-AT91SAM7X-PL, MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

AT91SAM-ICE, AT91-ISP, AT91SAM7XC-EK

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 8 Channel

For Use With

AT91SAM-ICE - EMULATOR FOR AT91 ARM7/ARM9AT91SAM7XC-EK - KIT EVAL FOR AT91SAM7XC256/128

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 529 of 727

- Download datasheet (11Mb)

37.3.2.2

37.3.2.3

6209F–ATARM–17-Feb-09

Auto Mode

PDC Mode

Table 37-1.

Note:

The Auto Mode is similar to Manual Mode, except that, as soon as the correct number of Input

Data registers is written, processing is automatically started without any action in the control

register.

The Peripheral Data Controller (PDC) can be used in association with the TDES to perform an

encryption/decryption of a buffer without any action by the software during processing.

In this starting mode, the type of the data transfer (byte, half-word or word) depends on the oper-

ation mode as per

Table 37-2.

The sequence is as follows:

Note:

• Set the START bit in the TDES Control register TDES_CR to begin the encryption or the

• When the processing completes, the bit DATRDY in the TDES Interrupt Status Register

• When the software reads one of the Output Data Registers (TDES_ODATAxR), the DATRDY

• Write the 64-bit key(s) in the different Key Word Registers (TDES_KEYxWxR), depending on

• Write the initialization vector (or counter) in the Initialization Vector Registers (TDES_IVxR).

decryption process.

(TDES_ISR) raises. If an interrupt has been enabled by setting the bit DATRDY in

TDES_IER, the interrupt line of the TDES is activated.

bit is automatically cleared.

whether one, two or three keys are required.

Operation Mode

CFB 64-bit

CFB 32-bit

CFB 16-bit

In 32-, 16- and 8-bit CFB mode, writing to TDES_IDATA2R register is not allowed and may lead to

errors in processing.

The Initialization Vector Registers concern all modes except ECB.

CFB 8-bit

OFB

Operation Mode

CFB 64-bit

CFB 32-bit

CFB 16-bit

Authorized Input Data Registers (Continued)

Data Transfer Type for Different Operation Modes

CFB 8-bit

ECB

CBC

OFB

Table

AT91SAM7XC512/256/128 Preliminary

37-2.

Input Data Registers to Write

TDES_IDATA1R

TDES_IDATA1R

TDES_IDATA1R

Data Transfer Type (PDC)

All

All

Half-word

Word

Word

Word

Word

Word

Byte

529

Related parts for AT91SAM7XC512-CU

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT EVAL FOR AT91SAM7XC256/128

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

KIT EVAL FOR AT91SAM7X256/128

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools KICKSTART KIT ATMEL AT91SAM7X

Manufacturer:

IAR Systems

Part Number:

Description:

MCU ARM9 64K SRAM 144-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM7 MCU FLASH 256K 100LQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MPU 217-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM9 ULTRA LOW PWR 217-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM9 324-TFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC MCU ARM9 SAMPLING 217CBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MCU 217-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MCU 208-PQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM 512K HS FLASH 100-LQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM 512K HS FLASH 100-TFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MCU 200 MHZ 324-TFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM MCU 16BIT 128K 256BGA

Manufacturer:

Atmel

Datasheet: