AT91SAM7XC512-CU Atmel, AT91SAM7XC512-CU Datasheet - Page 350

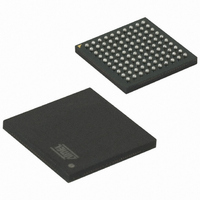

AT91SAM7XC512-CU

Manufacturer Part Number

AT91SAM7XC512-CU

Description

MCU ARM 512K HS FLASH 100-TFBGA

Manufacturer

Atmel

Series

AT91SAMr

Specifications of AT91SAM7XC512-CU

Core Processor

ARM7

Core Size

16/32-Bit

Speed

55MHz

Connectivity

CAN, Ethernet, I²C, SPI, SSC, UART/USART, USB

Peripherals

Brown-out Detect/Reset, DMA, POR, PWM, WDT

Number Of I /o

62

Program Memory Size

512KB (512K x 8)

Program Memory Type

FLASH

Ram Size

128K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 1.95 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-TFBGA

Processor Series

AT91SAMx

Core

ARM7TDMI

Data Bus Width

32 bit

Data Ram Size

128 KB

Interface Type

MII, SPI, TWI

Maximum Clock Frequency

55 MHz

Number Of Programmable I/os

62

Number Of Timers

3

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

JTRACE-ARM-2M, KSK-AT91SAM7X-PL, MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

AT91SAM-ICE, AT91-ISP, AT91SAM7XC-EK

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 8 Channel

For Use With

AT91SAM-ICE - EMULATOR FOR AT91 ARM7/ARM9AT91SAM7XC-EK - KIT EVAL FOR AT91SAM7XC256/128

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 350 of 727

- Download datasheet (11Mb)

Figure 31-4. Fractional Baud Rate Generator

31.6.1.4

31.6.1.5

350

SCK

Reserved

MCK/DIV

AT91SAM7XC512/256/128 Preliminary

MCK

Baud Rate in Synchronous Mode

Baud Rate in ISO 7816 Mode

USCLKS

0

1

2

3

If the USART is programmed to operate in synchronous mode, the selected clock is simply

divided by the field CD in US_BRGR.

In synchronous mode, if the external clock is selected (USCLKS = 3), the clock is provided

directly by the signal on the USART SCK pin. No division is active. The value written in

US_BRGR has no effect. The external clock frequency must be at least 4.5 times lower than the

system clock.

When either the external clock SCK or the internal clock divided (MCK/DIV) is selected, the

value programmed in CD must be even if the user has to ensure a 50:50 mark/space ratio on the

SCK pin. If the internal clock MCK is selected, the Baud Rate Generator ensures a 50:50 duty

cycle on the SCK pin, even if the value programmed in CD is odd.

The ISO7816 specification defines the bit rate with the following formula:

where:

• B is the bit rate

• Di is the bit-rate adjustment factor

• Fi is the clock frequency division factor

• f is the ISO7816 clock frequency (Hz)

BaudRate

16-bit Counter

CD

B

Modulus

=

Control

=

FP

SelectedClock

-----------------------------------------

Di

----- -

Fi

×

f

CD

glitch-free

USCLKS = 3

logic

FP

SYNC

0

CD

>1

1

0

1

0

OVER

Sampling

Divider

FIDI

0

1

6209F–ATARM–17-Feb-09

SYNC

SCK

Baud Rate

Sampling

Clock

Clock

Related parts for AT91SAM7XC512-CU

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT EVAL FOR AT91SAM7XC256/128

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

KIT EVAL FOR AT91SAM7X256/128

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools KICKSTART KIT ATMEL AT91SAM7X

Manufacturer:

IAR Systems

Part Number:

Description:

MCU ARM9 64K SRAM 144-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM7 MCU FLASH 256K 100LQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MPU 217-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM9 ULTRA LOW PWR 217-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM9 324-TFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC MCU ARM9 SAMPLING 217CBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MCU 217-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MCU 208-PQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM 512K HS FLASH 100-LQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM 512K HS FLASH 100-TFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MCU 200 MHZ 324-TFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM MCU 16BIT 128K 256BGA

Manufacturer:

Atmel

Datasheet: