AT91SAM7XC512-CU Atmel, AT91SAM7XC512-CU Datasheet - Page 193

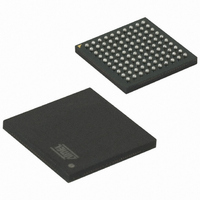

AT91SAM7XC512-CU

Manufacturer Part Number

AT91SAM7XC512-CU

Description

MCU ARM 512K HS FLASH 100-TFBGA

Manufacturer

Atmel

Series

AT91SAMr

Specifications of AT91SAM7XC512-CU

Core Processor

ARM7

Core Size

16/32-Bit

Speed

55MHz

Connectivity

CAN, Ethernet, I²C, SPI, SSC, UART/USART, USB

Peripherals

Brown-out Detect/Reset, DMA, POR, PWM, WDT

Number Of I /o

62

Program Memory Size

512KB (512K x 8)

Program Memory Type

FLASH

Ram Size

128K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 1.95 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-TFBGA

Processor Series

AT91SAMx

Core

ARM7TDMI

Data Bus Width

32 bit

Data Ram Size

128 KB

Interface Type

MII, SPI, TWI

Maximum Clock Frequency

55 MHz

Number Of Programmable I/os

62

Number Of Timers

3

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

JTRACE-ARM-2M, KSK-AT91SAM7X-PL, MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

AT91SAM-ICE, AT91-ISP, AT91SAM7XC-EK

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 8 Channel

For Use With

AT91SAM-ICE - EMULATOR FOR AT91 ARM7/ARM9AT91SAM7XC-EK - KIT EVAL FOR AT91SAM7XC256/128

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 193 of 727

- Download datasheet (11Mb)

24.7.7

6209F–ATARM–17-Feb-09

General Interrupt Mask

The AIC detects a spurious interrupt at the time the AIC_IVR is read while no enabled interrupt

source is pending. When this happens, the AIC returns the value stored by the programmer in

AIC_SPU (Spurious Vector Register). The programmer must store the address of a spurious

interrupt handler in AIC_SPU as part of the application, to enable an as fast as possible return to

the normal execution flow. This handler writes in AIC_EOICR and performs a return from

interrupt.

The AIC features a General Interrupt Mask bit to prevent interrupts from reaching the processor.

Both the nIRQ and the nFIQ lines are driven to their inactive state if the bit GMSK in AIC_DCR

(Debug Control Register) is set. However, this mask does not prevent waking up the processor if

it has entered Idle Mode. This function facilitates synchronizing the processor on a next event

and, as soon as the event occurs, performs subsequent operations without having to handle an

interrupt. It is strongly recommended to use this mask with caution.

• An internal interrupt source is programmed in level sensitive and the output signal of the

• An interrupt occurs just a few cycles before the software begins to mask it, thus resulting in a

corresponding embedded peripheral is activated for a short time. (As in the case for the

Watchdog.)

pulse on the interrupt source.

AT91SAM7XC512/256/128 Preliminary

193

Related parts for AT91SAM7XC512-CU

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT EVAL FOR AT91SAM7XC256/128

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

KIT EVAL FOR AT91SAM7X256/128

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools KICKSTART KIT ATMEL AT91SAM7X

Manufacturer:

IAR Systems

Part Number:

Description:

MCU ARM9 64K SRAM 144-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM7 MCU FLASH 256K 100LQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MPU 217-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM9 ULTRA LOW PWR 217-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM9 324-TFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC MCU ARM9 SAMPLING 217CBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MCU 217-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MCU 208-PQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM 512K HS FLASH 100-LQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM 512K HS FLASH 100-TFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MCU 200 MHZ 324-TFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM MCU 16BIT 128K 256BGA

Manufacturer:

Atmel

Datasheet: