AT91SAM7XC512-CU Atmel, AT91SAM7XC512-CU Datasheet - Page 557

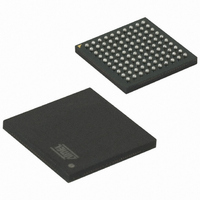

AT91SAM7XC512-CU

Manufacturer Part Number

AT91SAM7XC512-CU

Description

MCU ARM 512K HS FLASH 100-TFBGA

Manufacturer

Atmel

Series

AT91SAMr

Specifications of AT91SAM7XC512-CU

Core Processor

ARM7

Core Size

16/32-Bit

Speed

55MHz

Connectivity

CAN, Ethernet, I²C, SPI, SSC, UART/USART, USB

Peripherals

Brown-out Detect/Reset, DMA, POR, PWM, WDT

Number Of I /o

62

Program Memory Size

512KB (512K x 8)

Program Memory Type

FLASH

Ram Size

128K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 1.95 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-TFBGA

Processor Series

AT91SAMx

Core

ARM7TDMI

Data Bus Width

32 bit

Data Ram Size

128 KB

Interface Type

MII, SPI, TWI

Maximum Clock Frequency

55 MHz

Number Of Programmable I/os

62

Number Of Timers

3

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

JTRACE-ARM-2M, KSK-AT91SAM7X-PL, MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

AT91SAM-ICE, AT91-ISP, AT91SAM7XC-EK

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 8 Channel

For Use With

AT91SAM-ICE - EMULATOR FOR AT91 ARM7/ARM9AT91SAM7XC-EK - KIT EVAL FOR AT91SAM7XC256/128

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 557 of 727

- Download datasheet (11Mb)

Figure 38-5. CAN Bit Timing

6209F–ATARM–17-Feb-09

CAN Clock

MCK

SYNC_

t

CSC

SEG

The SAMPLE POINT is the point in time at which the bus level is read and interpreted as the

value of that respective bit. Its location is at the end of PHASE_SEG1.

The ReSynchronization Jump Width defines the limit to the amount of lengthening or shortening

of the Phase Segments.

SJW is programmable to be the minimum of PHASE SEG1 and 4 TQ.

If the SMP field in the CAN_BR register is set, then the incoming bit stream is sampled three

times with a period of half a CAN clock period, centered on sample point.

In the CAN controller, the length of a bit on the CAN bus is determined by the parameters (BRP,

PROPAG, PHASE1 and PHASE2).

The time quantum is calculated as follows:

Note: The BRP field must be within the range [1, 0x7F], i.e., BRP = 0 is not authorized.

To compensate for phase shifts between clock oscillators of different controllers on the bus, the

CAN controller must resynchronize on any relevant signal edge of the current transmission. The

resynchronization shortens or lengthens the bit time so that the position of the sample point is

shifted with regard to the detected edge. The resynchronization jump width (SJW) defines the

maximum of time by which a bit period may be shortened or lengthened by resynchronization.

Example of bit timing determination for CAN baudrate of 500 Kbit/s:

PROP_SEG

• SJW: ReSynchronization Jump Width.

t

PRS

MCK = 48MHz

CAN baudrate= 500kbit/s => bit time= 2us

t

t

BIT

CSC

t

t

t

PRS

PHS2

PHS1

t

SJW

=

=

=

t

AT91SAM7XC512/256/128 Preliminary

CSC

=

=

(

=

BRP

t

CSC

NOMINAL BIT TIME

t

t

t

CSC

CSC

CSC

PHASE_SEG1

+

t

×

+

PRS

×

×

×

t

1

(

PHS1

PROPAG

)

(

(

(

PHASE2

SJW

PHASE1

⁄

+

t

MCK

PHS1

+

1

+

)

+

+

+

t

1

PHS2

1

1

)

)

)

Sample Point

PHASE_SEG2

t

PHS2

Transmission Point

557

Related parts for AT91SAM7XC512-CU

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT EVAL FOR AT91SAM7XC256/128

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

KIT EVAL FOR AT91SAM7X256/128

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools KICKSTART KIT ATMEL AT91SAM7X

Manufacturer:

IAR Systems

Part Number:

Description:

MCU ARM9 64K SRAM 144-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM7 MCU FLASH 256K 100LQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MPU 217-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM9 ULTRA LOW PWR 217-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM9 324-TFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC MCU ARM9 SAMPLING 217CBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MCU 217-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MCU 208-PQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM 512K HS FLASH 100-LQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM 512K HS FLASH 100-TFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MCU 200 MHZ 324-TFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM MCU 16BIT 128K 256BGA

Manufacturer:

Atmel

Datasheet: