EP9315-IBZ Cirrus Logic Inc, EP9315-IBZ Datasheet - Page 81

EP9315-IBZ

Manufacturer Part Number

EP9315-IBZ

Description

32-Bit Microcontroller IC

Manufacturer

Cirrus Logic Inc

Series

EP9r

Specifications of EP9315-IBZ

Controller Family/series

(ARM9)

Core Size

32 Bit

A/d Converter

12 Bits

Supply Voltage

3.3V

No. Of I/o Pins

65

Package / Case

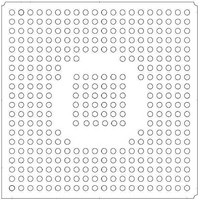

352-PBGA

Clock Frequency

200MHz

Core Processor

ARM9

Speed

200MHz

Connectivity

EBI/EMI, EIDE, Ethernet, I²C, IrDA, Keypad/Touchscreen, PCMCIA, SPI, UART/USART, USB

Peripherals

AC'97, DMA, I²:S, LCD, LED, MaverickKey, POR, PWM, WDT

Number Of I /o

16

Program Memory Type

ROMless

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 3.6 V

Data Converters

A/D 8x12b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Processor Series

EP93xx

Core

ARM920T

Data Bus Width

32 bit

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

EDB9315A-Z

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

598-1144 - KIT DEVELOPMENT EP9315 ARM9

Eeprom Size

-

Program Memory Size

-

Lead Free Status / Rohs Status

Details

Other names

598-1263

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

13

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

347

- Current page: 81 of 824

- Download datasheet (13Mb)

DS785UM1

DAID:

HVID:

ISAT:

UI:

INT:

AEXC:

Copyright 2007 Cirrus Logic

MaverickCrunch Architecture ID. This read-only value is

i n c r e m e n t e d f o r e a c h r e v i s i o n o f t h e o v e r a l l

MaverickCrunch co-processor architecture. These bits are

“000” for this revision.

Hardware Version ID. This read-only value is incremented

each time the hardware implementation of the architecture

named by DAID[2:0] is changed, typically done in

response to bugs. These bits are “000” for this version.

Integer Saturate Enable. This bit controls whether non-

a cc um u la to r int eg e r op e ra tio ns , bo th sig n ed an d

unsigned, will saturate on overflow or underflow:

0 = Saturation enabled

1 = Saturation disabled

Unsigned Integer Enable. This bit controls whether non-

accumulator integer operations treat their operands as

signed or unsigned. It also determines the saturation value

if the ISAT bit is clear:

0 = Signed integers

1 = Unsigned integers

MaverickCrunch Interrupt. This bit indicates whether an

interrupt has occurred. This bit is identical to the external

interrupt signal:

0 = No interrupt signaled

1 = Interrupt signaled

Asynchronous Exception Enable. This bit determines

whether exceptions generated by the co-processor are

sign aled syn chron ou sly or asyn chro nou sly to the

ARM920T. Synchronous exceptions force all data path

instructions to be serialized and to stall the ARM920T. If

exceptions are asynchronous, they are signalled by

assertion of the DSPINT output of the co-processor, which

may interrupt the ARM920T via the interrupt controller.

Enabling asynchronous exceptions does provide a

performance improvement, but makes it difficult for an

interrupt handler to determine the co-processor instruction

that caused the exception because the address of the

i n s t r u c t i o n i s n o t p r e s e r v e d . E x c e p t i o n s m a y b e

individually enabled by other bits in this register (IXE, UFE,

OFE, and IOE). This bit has no effect if no exceptions are

enabled:

0 = Exceptions are synchronous

1 = Exceptions are asynchronous

MaverickCrunch Co-Processor

EP93xx User’s Guide

3-11

3

Related parts for EP9315-IBZ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC ARM9 SOC ENH UNIV 352PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools Eval Bd Uni. ARM9 SOC Processor

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

High-efficiency PFC + Fluorescent Lamp Driver Reference Design

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Ref Bd For Speakerbar MSA & DSP Products

Manufacturer:

Cirrus Logic Inc