EP9315-IBZ Cirrus Logic Inc, EP9315-IBZ Datasheet - Page 128

EP9315-IBZ

Manufacturer Part Number

EP9315-IBZ

Description

32-Bit Microcontroller IC

Manufacturer

Cirrus Logic Inc

Series

EP9r

Specifications of EP9315-IBZ

Controller Family/series

(ARM9)

Core Size

32 Bit

A/d Converter

12 Bits

Supply Voltage

3.3V

No. Of I/o Pins

65

Package / Case

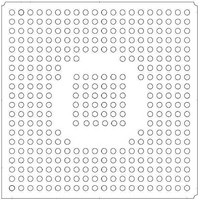

352-PBGA

Clock Frequency

200MHz

Core Processor

ARM9

Speed

200MHz

Connectivity

EBI/EMI, EIDE, Ethernet, I²C, IrDA, Keypad/Touchscreen, PCMCIA, SPI, UART/USART, USB

Peripherals

AC'97, DMA, I²:S, LCD, LED, MaverickKey, POR, PWM, WDT

Number Of I /o

16

Program Memory Type

ROMless

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 3.6 V

Data Converters

A/D 8x12b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Processor Series

EP93xx

Core

ARM920T

Data Bus Width

32 bit

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

EDB9315A-Z

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

598-1144 - KIT DEVELOPMENT EP9315 ARM9

Eeprom Size

-

Program Memory Size

-

Lead Free Status / Rohs Status

Details

Other names

598-1263

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

13

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

347

- Current page: 128 of 824

- Download datasheet (13Mb)

5

5-2

System Controller

EP93xx User’s Guide

5.1.3 Hardware Configuration Control

“Watchdog” on page 19-3

regarding which reset event occurred. Note that only the Watchdog timer contains

information about a user-generated 3-key reset.

The Hardware Configuration controls provide a mechanism to place the system into various

boot configurations. In addition, one of several external boot memory options can be selected

at system wake up.

The Hardware Configuration controls are defined by a set of device pins that are latched into

configuration control bits on the rising edge of the PRSTn or RSTOn pin. The different

hardware configuration bits define watchdog behavior, boot mode (internal or external), boot

synchronicity, and external boot width. The latched pins are described in

The latched version of these signals have an “L” prefix, are stored in the SysCfg register, and

are readable by software. Note that the signals EECLK and EEDAT may have 1 kΩ pull-up

resisters if used in an open-drain two-wire serial port application. (The default state

assignments will assume these pull-ups.)

The Hardware Control configurations are show in

Note: If PLLs are enabled, user reset does NOT disable or reset the PLLs. They retain their

• Three-key reset. When F2, F4, and F7 are pressed, a user reset occurs.

• Software reset and watchdog reset. They perform the functions of the user reset, but are

certain system variables such as RTC, SDRAM refresh control/global configuration, and

the Syscon registers.

under software control.

frequency settings.

Table 5-1. Hardware Configuration Control Latched Pins

CSn[1]

CSn[2]

CSn[3]

EECLK

EEDAT

BOOT[1:0]

ASDO

CSn[7:6]

Pin Name(s)

and

Copyright 2007 Cirrus Logic

“PwrSts” on page 5-14

Enable/Disable Watchdog

reset timer

reset duration

boot

asynchronous boot

Enable/Disable Watchdog

Should be pulled-up to “1”

Select internal or external

Should be pulled-up to “1”

Select boot mode

Select synchronous or

Select external boot width

Action

Table

registers contain the information

5-2.

Table

5-1.

DS785UM1

Related parts for EP9315-IBZ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC ARM9 SOC ENH UNIV 352PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools Eval Bd Uni. ARM9 SOC Processor

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

High-efficiency PFC + Fluorescent Lamp Driver Reference Design

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Ref Bd For Speakerbar MSA & DSP Products

Manufacturer:

Cirrus Logic Inc