EP9315-IBZ Cirrus Logic Inc, EP9315-IBZ Datasheet - Page 450

EP9315-IBZ

Manufacturer Part Number

EP9315-IBZ

Description

32-Bit Microcontroller IC

Manufacturer

Cirrus Logic Inc

Series

EP9r

Specifications of EP9315-IBZ

Controller Family/series

(ARM9)

Core Size

32 Bit

A/d Converter

12 Bits

Supply Voltage

3.3V

No. Of I/o Pins

65

Package / Case

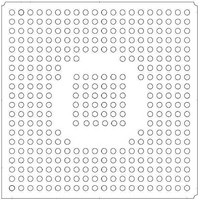

352-PBGA

Clock Frequency

200MHz

Core Processor

ARM9

Speed

200MHz

Connectivity

EBI/EMI, EIDE, Ethernet, I²C, IrDA, Keypad/Touchscreen, PCMCIA, SPI, UART/USART, USB

Peripherals

AC'97, DMA, I²:S, LCD, LED, MaverickKey, POR, PWM, WDT

Number Of I /o

16

Program Memory Type

ROMless

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 3.6 V

Data Converters

A/D 8x12b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Processor Series

EP93xx

Core

ARM920T

Data Bus Width

32 bit

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

EDB9315A-Z

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

598-1144 - KIT DEVELOPMENT EP9315 ARM9

Eeprom Size

-

Program Memory Size

-

Lead Free Status / Rohs Status

Details

Other names

598-1263

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

13

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

347

- Current page: 450 of 824

- Download datasheet (13Mb)

11

11-10

Universal Serial Bus Host Controller

EP93xx User’s Guide

11.2.5.4 HCI Master Block

11.2.5.5 USB State Control

11.2.5.6 Data FIFO

11.2.5.7 List Processor

11.2.5.8 Root Hub and Host SIE

The HCI Master Block handles read/write requests to system memory that are initiated by the

List Processor while the Host Controller (HC) is in the operational state and is processing the

lists queued in by HCD. It generates the addresses for all the memory accesses, which is the

DMA functionality. The major tasks handled by this block are:

This block implements:

This block contains a 64x8 FIFO to store the data returned by endpoints on IN tokens, and

the data to be sent to the endpoints on OUT Tokens. The FIFO is used as a buffer in case the

HC does not get timely access to the host bus.

The List Processor processes the lists scheduled by HCD according to the priority set in the

operational registers.

The Root Hub propagates Reset and Resume to downstream ports and handles port connect

and disconnect. The Host Serial Interface Engine (HSIE) converts parallel to serial, serial to

parallel, Non-Return to Zero Interface (NRZI) encoding/decoding and manages USB serial

protocol.

• Fetching Endpoint Descriptors (ED) and Transfer Descriptors (TD)

• Read/Write endpoint data from/to system memory

• Accessing HC Communication Area (HCCA)

• Write Status and Retire TDs

• The USB operational states of the Host Controller, as defined in the OHCI Specification.

• It generates SOF tokens every 1 ms

• It triggers the List Processor while HC is in the operational states.

Copyright 2007 Cirrus Logic

DS785UM1

Related parts for EP9315-IBZ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC ARM9 SOC ENH UNIV 352PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools Eval Bd Uni. ARM9 SOC Processor

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

High-efficiency PFC + Fluorescent Lamp Driver Reference Design

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Ref Bd For Speakerbar MSA & DSP Products

Manufacturer:

Cirrus Logic Inc