EP9315-IBZ Cirrus Logic Inc, EP9315-IBZ Datasheet - Page 320

EP9315-IBZ

Manufacturer Part Number

EP9315-IBZ

Description

32-Bit Microcontroller IC

Manufacturer

Cirrus Logic Inc

Series

EP9r

Specifications of EP9315-IBZ

Controller Family/series

(ARM9)

Core Size

32 Bit

A/d Converter

12 Bits

Supply Voltage

3.3V

No. Of I/o Pins

65

Package / Case

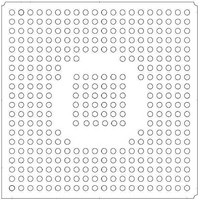

352-PBGA

Clock Frequency

200MHz

Core Processor

ARM9

Speed

200MHz

Connectivity

EBI/EMI, EIDE, Ethernet, I²C, IrDA, Keypad/Touchscreen, PCMCIA, SPI, UART/USART, USB

Peripherals

AC'97, DMA, I²:S, LCD, LED, MaverickKey, POR, PWM, WDT

Number Of I /o

16

Program Memory Type

ROMless

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 3.6 V

Data Converters

A/D 8x12b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Processor Series

EP93xx

Core

ARM920T

Data Bus Width

32 bit

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

EDB9315A-Z

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

598-1144 - KIT DEVELOPMENT EP9315 ARM9

Eeprom Size

-

Program Memory Size

-

Lead Free Status / Rohs Status

Details

Other names

598-1263

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

13

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

347

- Current page: 320 of 824

- Download datasheet (13Mb)

9

Receive Status - First Word

9-18

1/10/100 Mbps Ethernet LAN Controller

EP93xx User’s Guide

9.2.3.1 Receive Status Format

CRCI

RFP

31

15

Definition:

Bit Descriptions:

If both EOF and EOB bits are zero, the entry was made for a receive header threshold. This

indicates that there have been at least as many bytes transferred as specified in Receive

Header Length 1 or 2. These registers may be set to any threshold to provide an early

indication to the Host that a receive frame is in progress. The status will contain valid data in

the address match and hash table fields, but as the status is provided before end of frame is

reached, it will always indicate received without error.

If the EOF bit is zero and the EOB bit is set, the status indicates that the end of a receive

buffer has been reached before the end of the receive frame. If the receive buffers are much

smaller than the frame size, there may be many such statuses per frame.

When the EOF and EOB bits are both set, the status indicates the end of frame has been

transferred. The EOB is always set at this time to indicate that the MAC has finished

transferring to the buffer. The buffer is not necessarily full.

When a status event causes an interrupt, the interrupt pin will be activated after the status

has been transferred to the status queue.

RSVD

RWE

30

14

EOF

29

13

EOB

28

12

Receive Status, first word. Contains status information for the receiver

operation.

RSVD:

RFP:

RWE:

27

11

HTI

26

10

RSVD

Copyright 2007 Cirrus Logic

25

9

Reserved. Unknown During Read.

Receive Frame Processed. The Receive Frame

Processed bit is always written as a “1” by the MAC when

the status is ready and it may be used by the Host to mark

its progress through the status queue. The Host may

alternatively use the RXStsQCurAdd to determine how

much of the status queue to process.

Received Without Error. The Received Without Error bit

indicates that the frame was received without any of the

following error conditions: CRCerror, ExtraData, Runt, or

Receive Overrun.

24

8

23

7

AM

22

6

RX_Err

21

5

OE

20

4

RSVD

FE

19

3

Runt

18

2

EData

17

1

DS785UM1

CRCE

16

0

Related parts for EP9315-IBZ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC ARM9 SOC ENH UNIV 352PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools Eval Bd Uni. ARM9 SOC Processor

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

High-efficiency PFC + Fluorescent Lamp Driver Reference Design

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Ref Bd For Speakerbar MSA & DSP Products

Manufacturer:

Cirrus Logic Inc