EP9315-IBZ Cirrus Logic Inc, EP9315-IBZ Datasheet - Page 502

EP9315-IBZ

Manufacturer Part Number

EP9315-IBZ

Description

32-Bit Microcontroller IC

Manufacturer

Cirrus Logic Inc

Series

EP9r

Specifications of EP9315-IBZ

Controller Family/series

(ARM9)

Core Size

32 Bit

A/d Converter

12 Bits

Supply Voltage

3.3V

No. Of I/o Pins

65

Package / Case

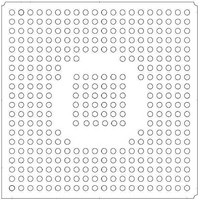

352-PBGA

Clock Frequency

200MHz

Core Processor

ARM9

Speed

200MHz

Connectivity

EBI/EMI, EIDE, Ethernet, I²C, IrDA, Keypad/Touchscreen, PCMCIA, SPI, UART/USART, USB

Peripherals

AC'97, DMA, I²:S, LCD, LED, MaverickKey, POR, PWM, WDT

Number Of I /o

16

Program Memory Type

ROMless

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 3.6 V

Data Converters

A/D 8x12b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Processor Series

EP93xx

Core

ARM920T

Data Bus Width

32 bit

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

EDB9315A-Z

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

598-1144 - KIT DEVELOPMENT EP9315 ARM9

Eeprom Size

-

Program Memory Size

-

Lead Free Status / Rohs Status

Details

Other names

598-1263

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

13

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

347

- Current page: 502 of 824

- Download datasheet (13Mb)

13

13-6

SDRAM, SyncROM, and SyncFLASH Controller

EP93xx User’s Guide

13.5 Programming Mode Register: SDRAM Or SyncROM Device

Mapped addr for

default 32-bit

wide

SDRAM or

SFLASH

Example:

SDRAM with

WBM = 0,

OM= 0,

CASL = 3,

BT = Sequential,

BL = 4

SROM

Example: SROM

RAS =2, CAS=2,

Sequential, BL=4

Address

When setting up the Mode register that is inside an SDRAM or SyncROM device, or the

Configuration register that is inside a SyncFLASH device, the command word that is placed

on the address pins shown in

SyncFlash is attached. Once Initialize = ‘0’, MRS = ‘1’, and LCR = ‘0’ are written to the

GlConfig register to enable access to the Mode register, the address of a subsequent Read

operation is output on AD[12:0]. The internal address, A[23:0], is mapped to external address

pins AD[12:0] as shown in

In

configurations must be set to four. The Burst Length for 16-bit configurations must be set to

eight. See

AD[3] specifies Burst Type (BT). A value of zero specifies Sequential, a value of one specifies

Interleaved.

AD[6:4] specifies CAS Latency (CASL). Only values of two or three are supported. See

Table 13-6

AD[8:7] specify Operation Mode (OM). This value must be zero for normal operation.

AD[9] specifies the Write Burst Mode (WBM). This value should be programmed to zero for

devices that support burst, such as SDRAM. It should be set to zero for devices that do not

support burst mode, such as SyncFlash or SyncROM.

AD[12:10] are reserved, but must be zero for normal operation.

Note: If using an external bus that is 16 bits wide then the address mapping must be shifted as

Note: For SDRAM, AD[2:0] specify burst length. For SROM, AD[1:0] specify burst length.

Table

indicated by

AD12 AD11 AD10 AD9

13-5, AD[2:0] represents the Burst Length (BL). The Burst Length for 32-bit

A22

Table 13-5. Mode Register Command Decoding for 32-bit Wide Memory Bus

0

0

Table 13-8

for CAS Latency values.

RFU

A21

0

0

Table 13-3 on page

A20

0

0

RFU

for Burst Length values.

Mode

Write

Burst

A19

Table

0

0

Table 13-5

Copyright 2007 Cirrus Logic

13-5.

AD8

A18

0

0

Operating

13-4.

Mode

depends on whether a SROM, SDRAM, or

AD7

RFU

A17

0

0

AD6

RAS

A16

0

1

CAS Latency

AD5

A15

1

1

CAS

AD4

A14

1

0

Burst

AD3

Type

A13

0

0

AD2 AD1 AD0

Burst

Type

A12

0

0

0

DS785UM1

A11

1

1

0

0

A10

0

0

1

1

Related parts for EP9315-IBZ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC ARM9 SOC ENH UNIV 352PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools Eval Bd Uni. ARM9 SOC Processor

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

High-efficiency PFC + Fluorescent Lamp Driver Reference Design

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Ref Bd For Speakerbar MSA & DSP Products

Manufacturer:

Cirrus Logic Inc