EP9315-IBZ Cirrus Logic Inc, EP9315-IBZ Datasheet - Page 305

EP9315-IBZ

Manufacturer Part Number

EP9315-IBZ

Description

32-Bit Microcontroller IC

Manufacturer

Cirrus Logic Inc

Series

EP9r

Specifications of EP9315-IBZ

Controller Family/series

(ARM9)

Core Size

32 Bit

A/d Converter

12 Bits

Supply Voltage

3.3V

No. Of I/o Pins

65

Package / Case

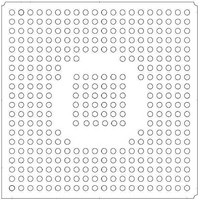

352-PBGA

Clock Frequency

200MHz

Core Processor

ARM9

Speed

200MHz

Connectivity

EBI/EMI, EIDE, Ethernet, I²C, IrDA, Keypad/Touchscreen, PCMCIA, SPI, UART/USART, USB

Peripherals

AC'97, DMA, I²:S, LCD, LED, MaverickKey, POR, PWM, WDT

Number Of I /o

16

Program Memory Type

ROMless

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 3.6 V

Data Converters

A/D 8x12b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Processor Series

EP93xx

Core

ARM920T

Data Bus Width

32 bit

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

EDB9315A-Z

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

598-1144 - KIT DEVELOPMENT EP9315 ARM9

Eeprom Size

-

Program Memory Size

-

Lead Free Status / Rohs Status

Details

Other names

598-1263

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

13

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

347

- Current page: 305 of 824

- Download datasheet (13Mb)

DS785UM1

9.1.2 MAC Engine

9.1.2.1 Data Encapsulation

The RAM blocks are interleaved in the AHB address space. AHB address bits 0 and 1 are

byte selects and must be zero for direct access. AHB address bit 2 selects the left or right

RAM array, which is the Transmit or Receive array. AHB address bits 3,4, and 5 perform a 1-

of-8 column select. Address bit 6 selects the even or odd row address. Address bits 7, 8, 9,

and 10 decode the rows. Thus from an AHB addressing perspective, the MAC FIFOs are one

large RAM array.

Table 9-1

are in byte units. All data transfers to the FIFO RAM are restricted to words.

Caution: Accessing the FIFO RAM while the MAC is operating will likely cause a

malfunction.

There is no arbitration logic between direct AHB access and MAC Descriptor Processor

access.

The MAC configurations registers and FIFO RAMs are only word accessible

The MAC engine is compliant with the requirements of ISO/IEC 8802-3 (1993), Sections 3

and 4.

In transmission, the MAC automatically prepends the preamble, and computes and appends

the FCS. The data after the SFD and before the FCS is supplied by the host as the

transmitted data. FCS generation by the MAC may be disabled by setting InhibitCRC bit in

the Transmit Frame Descriptor. Refer to

defines the FIFO RAM address map as it appears in the address space. Address

0x8001_4800 to 0x8001_4FFF

0x8001_5080 to 0x8001_50BF

0x8001_50C0 to 0x8001_50FF

0x8001_4000 to 0x8001_47FF

0x8001_5000 to 0x8001_503F

0x8001_5040 to 0x8001_507F

FIFO RAM Address Map

Copyright 2007 Cirrus Logic

Table 9-1. FIFO RAM Address Map

Figure

9-2.

1/10/100 Mbps Ethernet LAN Controller

Rx Descriptor

Tx Descriptor

Rx Status

Tx Status

Rx Data

Tx Data

Usage

EP93xx User’s Guide

9-3

9

Related parts for EP9315-IBZ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC ARM9 SOC ENH UNIV 352PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools Eval Bd Uni. ARM9 SOC Processor

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

High-efficiency PFC + Fluorescent Lamp Driver Reference Design

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Ref Bd For Speakerbar MSA & DSP Products

Manufacturer:

Cirrus Logic Inc