EP9315-IBZ Cirrus Logic Inc, EP9315-IBZ Datasheet - Page 7

EP9315-IBZ

Manufacturer Part Number

EP9315-IBZ

Description

32-Bit Microcontroller IC

Manufacturer

Cirrus Logic Inc

Series

EP9r

Specifications of EP9315-IBZ

Controller Family/series

(ARM9)

Core Size

32 Bit

A/d Converter

12 Bits

Supply Voltage

3.3V

No. Of I/o Pins

65

Package / Case

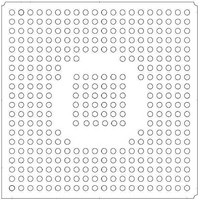

352-PBGA

Clock Frequency

200MHz

Core Processor

ARM9

Speed

200MHz

Connectivity

EBI/EMI, EIDE, Ethernet, I²C, IrDA, Keypad/Touchscreen, PCMCIA, SPI, UART/USART, USB

Peripherals

AC'97, DMA, I²:S, LCD, LED, MaverickKey, POR, PWM, WDT

Number Of I /o

16

Program Memory Type

ROMless

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 3.6 V

Data Converters

A/D 8x12b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Processor Series

EP93xx

Core

ARM920T

Data Bus Width

32 bit

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

EDB9315A-Z

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

598-1144 - KIT DEVELOPMENT EP9315 ARM9

Eeprom Size

-

Program Memory Size

-

Lead Free Status / Rohs Status

Details

Other names

598-1263

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

13

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

347

- Current page: 7 of 824

- Download datasheet (13Mb)

Chapter 9. 1/10/100 Mbps Ethernet LAN Controller ........................................... 9-1

DS785UM1

8.7 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-22

9.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-1

9.2 Descriptor Processor. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-13

9.3 Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-40

8.6.4 Block Copy Function......................................................................................................8-18

9.1.1 Detailed Description ........................................................................................................9-1

9.1.2 MAC Engine ....................................................................................................................9-3

9.1.3 Packet Transmission Process .........................................................................................9-5

9.1.4 Transmit Back-Off............................................................................................................9-7

9.2.1 Receive Descriptor Processor Queues .........................................................................9-13

9.2.2 Receive Descriptor Queue ............................................................................................9-13

9.2.3 Receive Status Queue...................................................................................................9-16

9.2.4 Interrupts .......................................................................................................................9-37

9.2.5 Initialization....................................................................................................................9-37

8.6.4.1 Example of Block Copy................................................................................8-21

9.1.1.1 Host Interface and Descriptor Processor .......................................................9-1

9.1.1.2 Reset and Initialization...................................................................................9-2

9.1.1.3 Power-down Modes .......................................................................................9-2

9.1.1.4 Address Space ..............................................................................................9-2

9.1.2.1 Data Encapsulation........................................................................................9-3

9.1.3.1 Carrier Deference ..........................................................................................9-5

9.1.4.1 Transmission .................................................................................................9-7

9.1.4.2 The FCS Field................................................................................................9-7

9.1.4.3 Bit Order ........................................................................................................9-8

9.1.4.4 Destination Address (DA) Filter .....................................................................9-8

9.1.4.5 Perfect Address Filtering ...............................................................................9-8

9.1.4.6 Hash Filter .....................................................................................................9-9

9.1.4.7 Flow Control.................................................................................................9-10

9.1.4.8 Receive Flow Control...................................................................................9-10

9.1.4.9 Transmit Flow Control..................................................................................9-10

9.1.4.10 Rx Missed and Tx Collision Counters ........................................................9-11

9.1.4.11 Accessing the MII ......................................................................................9-11

9.2.3.1 Receive Status Format ................................................................................9-18

9.2.3.2 Receive Flow ...............................................................................................9-21

9.2.3.3 Receive Errors .............................................................................................9-22

9.2.3.4 Receive Descriptor Data/Status Flow ..........................................................9-23

9.2.3.5 Receive Descriptor Example .......................................................................9-24

9.2.3.6 Receive Frame Pre-Processing...................................................................9-25

9.2.3.7 Transmit Descriptor Processor Queues.......................................................9-26

9.2.3.8 Transmit Descriptor Queue..........................................................................9-26

9.2.3.9 Transmit Descriptor Format .........................................................................9-28

9.2.3.10 Transmit Status Queue..............................................................................9-30

9.2.3.11 Transmit Status Format .............................................................................9-32

9.2.3.12 Transmit Flow ............................................................................................9-34

9.2.3.13 Transmit Errors ..........................................................................................9-35

9.2.3.14 Transmit Descriptor Data/Status Flow .......................................................9-36

9.2.4.1 Interrupt Processing.....................................................................................9-37

9.2.5.1 Interrupt Processing.....................................................................................9-38

9.2.5.2 Receive Queue Processing .........................................................................9-38

9.2.5.3 Transmit Queue Processing ........................................................................9-38

9.2.5.4 Other Processing .........................................................................................9-38

9.2.5.5 Transmit Restart Process ............................................................................9-39

©

Copyright 2007 Cirrus Logic, Inc.

EP93xx User’s Guide

vii

Related parts for EP9315-IBZ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC ARM9 SOC ENH UNIV 352PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools Eval Bd Uni. ARM9 SOC Processor

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

High-efficiency PFC + Fluorescent Lamp Driver Reference Design

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Ref Bd For Speakerbar MSA & DSP Products

Manufacturer:

Cirrus Logic Inc