EP9315-IBZ Cirrus Logic Inc, EP9315-IBZ Datasheet - Page 397

EP9315-IBZ

Manufacturer Part Number

EP9315-IBZ

Description

32-Bit Microcontroller IC

Manufacturer

Cirrus Logic Inc

Series

EP9r

Specifications of EP9315-IBZ

Controller Family/series

(ARM9)

Core Size

32 Bit

A/d Converter

12 Bits

Supply Voltage

3.3V

No. Of I/o Pins

65

Package / Case

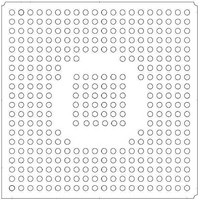

352-PBGA

Clock Frequency

200MHz

Core Processor

ARM9

Speed

200MHz

Connectivity

EBI/EMI, EIDE, Ethernet, I²C, IrDA, Keypad/Touchscreen, PCMCIA, SPI, UART/USART, USB

Peripherals

AC'97, DMA, I²:S, LCD, LED, MaverickKey, POR, PWM, WDT

Number Of I /o

16

Program Memory Type

ROMless

Ram Size

32K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 3.6 V

Data Converters

A/D 8x12b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Processor Series

EP93xx

Core

ARM920T

Data Bus Width

32 bit

3rd Party Development Tools

MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

EDB9315A-Z

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

598-1144 - KIT DEVELOPMENT EP9315 ARM9

Eeprom Size

-

Program Memory Size

-

Lead Free Status / Rohs Status

Details

Other names

598-1263

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

13

Company:

Part Number:

EP9315-IBZ

Manufacturer:

CIRRUS

Quantity:

347

- Current page: 397 of 824

- Download datasheet (13Mb)

DS785UM1

10.1.3 DMA Operations

10.1.3.1 Memory-to-Memory Channels

The DMA controller memory-to-memory channels can also be used in “Memory to External

Peripheral” mode with handshaking protocol. A set of external handshake signals DREQ,

DACK and TC/DEOT are provided for each of 2 M2M channels.

Transfer is completed either on DEOT being asserted by the external peripheral or the byte

count expiring. Status bits will indicate if the actual byte count is equal to the programmed

limit, and also if the count was terminated by peripheral asserting DEOT. Completion of

transfer will cause a DMA interrupt on that channel and rollover to the “other” buffer

descriptor if configured.

For byte or word wide peripherals, the DMA will be programmed to request byte or word wide

AHB transfers respectively. The DMA will not issue an AHB HREQ for a transfer until it has

sampled DREQ asserted after DACK of the previous transfer has been asserted for the

duration of the programmed wait states in the SMC (and possibly DREQ is sampled in the

cycle DACK is deasserted).

The operation of the DMA controller can be defined in terms of channel functionality. Two

types of channels exist:

The two M2M channels support data transfers between:

• DREQ (input) can be programmed edge or level active, and active high or low. The

• DACK (output) can be programmed active high or low. DACK will cycle with each read

• TC/DEOT is a bidirectional signal, the direction and the active sense is programmable.

• Memory-to-Memory (M2M) channel

• Memory-to/from-Internal-Peripheral (M2P/P2M) channel.

• Memory locations which may be located in any accessible system memory banks.

• Memory locations related to IDE or SSP.

peripheral may hold DREQ active for the duration of the block transfers or may

assert/deassert on each transfer.

or write, the timing is to coincide with the nOE or nWE of the EBI.

When configured as an output, the DMA will assert TC (Terminal Count) on the final

transfer to coincide with the DACK, typically when the byte count has expired. When

configured as an input, the peripheral must assert DEOT concurrent with DREQ for the

final transfer in the block.

transfer will begin as soon as the channel is configured and enabled for memory to

memory move. For this transfer type, the DMA first fills the internal 16-byte data bay by

initiating read accesses on the source bus. It then empties the data from the data bay to

the destination bus by initiating write accesses.

These memory to memory moves can be initiated by software, in which case the

Copyright 2007 Cirrus Logic

EP93xx User’s Guide

DMA Controller

10-3

10

Related parts for EP9315-IBZ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC ARM9 SOC ENH UNIV 352PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

IC ARM920T MCU 200MHZ 352-PBGA

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools Eval Bd Uni. ARM9 SOC Processor

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

High-efficiency PFC + Fluorescent Lamp Driver Reference Design

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Development Kit

Manufacturer:

Cirrus Logic Inc

Datasheet:

Part Number:

Description:

Ref Bd For Speakerbar MSA & DSP Products

Manufacturer:

Cirrus Logic Inc